# Tesis de Doctorado en Ingeniería

Circuitos Integrados de Bajo Consumo para Arquitecturas de Redes Neuronales Profundas

Nicolás Daniel Rodríguez

Director: Pedro Marcelo Julián / Co-director: Eduardo Emilio Paolini

### Prefacio

Esta tesis se presenta como parte de los requisitos para optar al grado Académico de Doctor en Ingeniería, de la Universidad Nacional del Sur y no ha sido presentada previamente para la obtención de otro título en esta Universidad u otra. La misma contiene los resultados obtenidos en investigaciones llevadas a cabo en el ámbito del Departamento de Ingeniería Eléctrica y de Computadoras (DIEC) durante el período comprendido entre el 1 de Abril de 2018 y el 16 de Octubre de 2024, bajo la dirección del Dr. Pedro Marcelo Julian y del Ing. Eduardo Emilio Paolini, pertenecientes al Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages" (UNS-CONICET) y al Departamento de Ingeniería Eléctrica y de Computadoras de la Universidad Nacional del Sur.

Bahía Blanca, 16 de Octubre de 2024

Ing. Nicolás Daniel Rodríguez

#### UNIVERSIDAD NACIONAL DEL SUR Subsecretaría de Posgrado

La presente tesis ha sido aprobada el ...05/.03./2025..., mereciendo la calificación de ...10 (...diez....)

## Agradecimientos

Quisiera dedicar esta tesis a mi familia, amigos y colegas, quienes me brindaron su incondicional apoyo a lo largo de todos estos años. Agradezco profundamente a mis supervisores por su guía y apoyo durante este largo viaje, cuyo acompañamiento fue clave para la culminación de este trabajo. También quiero expresar mi gratitud a Silicon Austria Labs, ya que desde que me uní a la organización, mi investigación ha avanzado significativamente, gracias a los recursos disponibles y, sobre todo, a las incontables discusiones y sugerencias de mis colegas, cuyo profesionalismo y dedicación han sido una fuente constante de inspiración y motivación. Finalmente, deseo agradecer a mi madre, abuela y esposa, quienes son las personas más importantes e influyentes en mi vida. Sin su amor, fortaleza y sabiduría, este logro no habría sido posible.

#### Resumen

Esta tesis se enfoca en el desarrollo e implementación de aceleradores en circuitos integrados de uso específico (ASIC) para la ejecución eficiente de Redes Neuronales Profundas (DNN). Estas redes se caracterizan por involucrar una gran cantidad de datos, tanto de parámetros como de entradas, por lo que resulta imprescindible no solo un cómputo energéticamente eficiente, sino también un balance óptimo entre la transferencia de datos y el procesamiento. Para ello, en este trabajo se propone un algoritmo Simplicial Simétrico a Canales Separados (ChSymSim), que produce implementaciones de bajo consumo, y se optimiza una arquitectura que permite soportar la ejecución de distintos tipos de capas (diversas configuraciones de precisión, kernel, stride y padding) manteniendo la eficiencia energética.

Para poner en evidencia el impacto de la implementación, se realizaron dos prototipos preliminares con estructuras de prueba y evaluación (I/O de datos, buses, configuración, control) y se culminó con la fabricación de un sistema en *chip* (SoC) complejo de 9mm² en una tecnología de 65nm. Adicionalmente, se desarrollaron técnicas de entrenamiento con cuantización (QAT), optimizadas para funciones Simpliciales Simétricas en punto fijo.

Los experimentos realizados mostraron una eficiencia energética elevada, alcanzando valores promedios superiores a los 4 TOPS/W bajo diversas configuraciones, con un máximo de 12,12 TOPS/W. Estos resultados permiten asegurar que el acelerador ChSymSim propuesto es una solución viable para el procesamiento eficiente de algoritmos para aprendizaje de máquina (ML) en dispositivos embebidos de baja potencia.

### Abstract

This thesis focuses on the development and implementation of accelerators in application-specific integrated circuits (ASIC) for the efficient execution of Deep Neural Networks (DNN). These networks involve a large amount of data, both in terms of parameters and inputs, making it essential to achieve not only energy-efficient processing but also an optimal balance between data transfer and computation. To this end, this work proposes a Channel-wise Symmetric Simplicial algorithm (ChSymSim), which yields low-power implementations, and optimizes an architecture that supports the execution of different types of layers (various configurations of precision, kernel, stride, and padding) while maintaining energy efficiency.

To highlight the impact of the implementation, two preliminary prototypes were developed with testing and evaluation structures (data I/O, buses, configuration, control), culminating in the fabrication of a complex system-on-chip (SoC), with an area of 9mm<sup>2</sup> in a 65nm technology. Additionally, quantization-aware training (QAT) techniques were developed, optimized for Symmetric Simplicial functions in fixed-point arithmetic.

The experiments conducted showed high energy efficiency, achieving average values above 4 TOPS/W under various configurations, with a maximum of 12,12 TOP-S/W. These results confirm that the proposed ChSymSim accelerator is a viable solution for the efficient processing of machine learning (ML) algorithms in low-power embedded devices.

# Índice general

| Pı             | refaci | О                                              |   |  |  |  |  |  | 1  |

|----------------|--------|------------------------------------------------|---|--|--|--|--|--|----|

| A              | grade  | ecimientos                                     |   |  |  |  |  |  | 3  |

| Re             | esum   | en                                             |   |  |  |  |  |  | 4  |

| $\mathbf{A}$ l | bstra  | $\operatorname{ct}$                            |   |  |  |  |  |  | 5  |

| Ín             | dice   | de figuras                                     |   |  |  |  |  |  | 9  |

| Ín             | dice   | de tablas                                      |   |  |  |  |  |  | 21 |

| A              | cróni  | mos                                            |   |  |  |  |  |  | 25 |

| 1.             | Intr   | oducción                                       |   |  |  |  |  |  | 31 |

|                | 1.1.   | Problemática y estado del arte                 |   |  |  |  |  |  | 31 |

|                | 1.2.   | Objetivo                                       |   |  |  |  |  |  | 34 |

|                | 1.3.   | Contribución                                   |   |  |  |  |  |  | 36 |

|                | 1.4.   | Organización                                   |   |  |  |  |  |  | 39 |

|                | 1.5.   | Metodología                                    |   |  |  |  |  |  | 40 |

|                | 1.6.   | Publicaciones                                  | • |  |  |  |  |  | 40 |

| 2.             | Con    | ceptos Preliminares                            |   |  |  |  |  |  | 42 |

|                | 2.1.   | Procesamiento de imágenes y Machine Learning   |   |  |  |  |  |  | 43 |

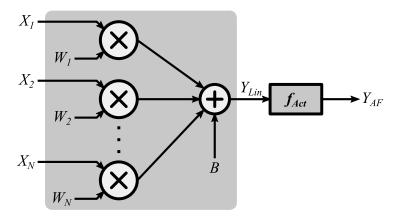

|                |        | 2.1.1. Perceptrón y funciones de activación    |   |  |  |  |  |  | 44 |

|                |        | 2.1.2. Entrenamiento de una neurona artificial |   |  |  |  |  |  | 47 |

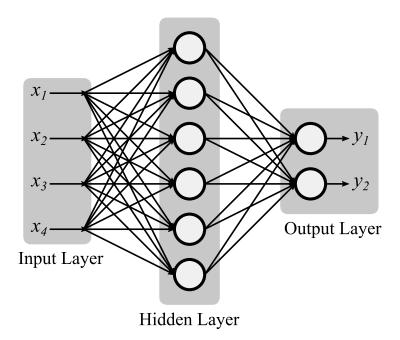

|                |        | 2.1.3. Redes neuronales profundas              |   |  |  |  |  |  | 51 |

|                |        | 2.1.4. Redes neuronales convolucionales        |   |  |  |  |  |  | 55 |

|            |      | 2.1.5. Operadores morfológicos                     | 60  |

|------------|------|----------------------------------------------------|-----|

|            | 2.2. | Cuantización                                       | 63  |

|            | 2.3. | Funciones simpliciales                             | 69  |

| 3.         | Fun  | ciones simpliciales aplicadas a Redes Neuronales   | 77  |

|            | 3.1. | Backpropagation en funciones simpliciales          | 78  |

|            | 3.2. | Algoritmo simplicial simétrico a canales separados | 85  |

|            | 3.3. | Inicialización de parámetros                       | 92  |

|            | 3.4. | Redes Neuronales simpliciales simétricas           | 97  |

|            |      | 3.4.1. RSSNN                                       | 98  |

|            |      | 3.4.2. SymSim DMN                                  | 01  |

|            |      | 3.4.3. ChSymSim ResNets                            | 105 |

|            | 3.5. | Conclusiones                                       | 12  |

| 4.         | Mod  | lelado de arquitecturas 1                          | 13  |

|            | 4.1. | Descripción del operador ChSymSim                  | .15 |

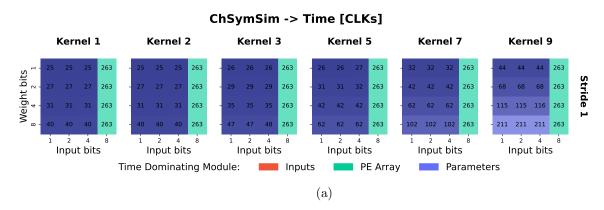

|            | 4.2. | Modelos de alto nivel                              | 29  |

|            |      | 4.2.1. Eficiencia de no-solapamiento               | 130 |

|            |      | 4.2.2. Análisis y modelado temporal                | 133 |

|            |      | 4.2.3. Estimación de área                          | 40  |

|            |      | 4.2.4. Consumo de potencia y energía               | 46  |

|            | 4.3. | Operador ChSymSim vs. lineal                       | 151 |

|            |      | 4.3.1. Comparación con modelos de alto nivel       | .51 |

|            |      | 4.3.2. Síntesis y resultados de simulación         | .58 |

|            | 4.4. | Conclusiones                                       | 168 |

| <b>5</b> . | Imp  | lementaciones en circuitos integrados 1            | 69  |

|            | 5.1. | Versiones preliminares                             | 171 |

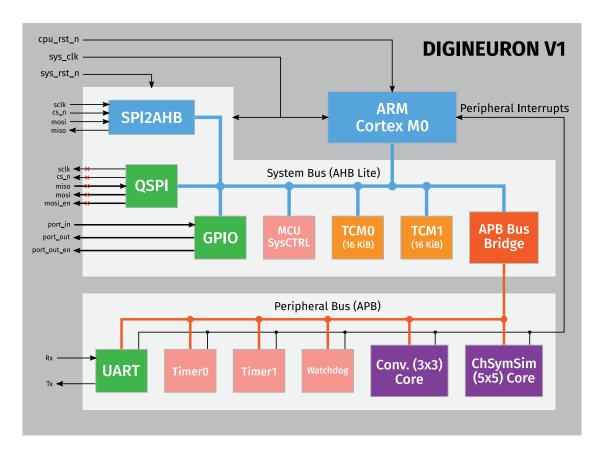

|            |      | 5.1.1. DigineuronV1                                | 171 |

|            |      | 5.1.2. DigineuronV2                                | 177 |

|            | 5.2. | Versión final: DigineuronV3a                       | 81  |

|            | 5.3. | Resultados experimentales                          | 92  |

|            |      | 5.3.1 Evaluación de los SoCs fabricados            | 09  |

|               |                | 5.3.2. Mediciones y desempeño                | 200         |

|---------------|----------------|----------------------------------------------|-------------|

|               | 5.4.           | Conclusiones                                 | 214         |

| 6.            | Con            | aclusiones                                   | <b>21</b> 5 |

| Bi            | bliog          | grafía                                       | 218         |

| Α.            | Pro            | piedades útiles de Esperanza y Varianza      | 227         |

| В.            | ReL            | uU en variables aleatorias                   | 229         |

|               | B.1.           | Capas ReLU tradicionales                     | 229         |

|               | B.2.           | Capas PReLU                                  | 232         |

|               | В.3.           | Capas ReLU con saturación                    | 233         |

| $\mathbf{C}.$ | Inic           | ialización de capas simpliciales simétricas  | 236         |

|               | C.1.           | Modo forward                                 | 236         |

|               | C.2.           | Modo backward                                | 244         |

| D.            | $\mathbf{Arq}$ | uitecturas ResNet                            | 248         |

| Ε.            | Uni            | dades de escalado, redondeo y ReLU           | <b>25</b> 3 |

| $\mathbf{F}.$ | Opt            | imizaciones de selectores en <i>hardware</i> | 257         |

| G.            | Con            | exionado de los SoC fabricados               | <b>26</b> 3 |

| н.            | Dig            | ineuronV3a: Mapas de memoria del SoC         | 268         |

| I.            | Maj            | pas de memoria del acelerador ChSymSim       | <b>27</b> 3 |

| J.            | Dig            | ineuronV3a: mediciones de consumo            | 289         |

| K.            | Dig            | ineuronV3a: desempeño y eficiencia           | 300         |

# Índice de figuras

| 2.1.  | Diagrama en bloques del modelo de neurona artificial                          | 44 |

|-------|-------------------------------------------------------------------------------|----|

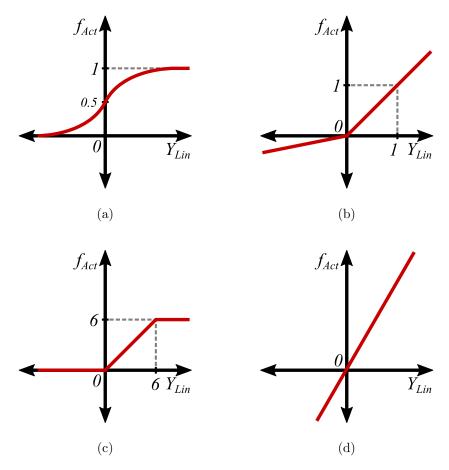

| 2.2.  | Ejemplos de funciones de activación: a) Sigmoide; b) PReLU; c) Re-            |    |

|       | LU6; d) Lineal                                                                | 45 |

| 2.3.  | Red Neuronal poco profunda (Shallow Network o SLFN)                           | 46 |

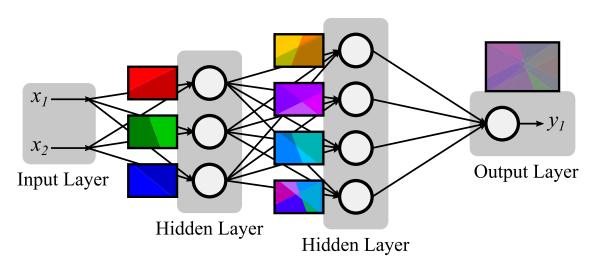

| 2.4.  | Ejemplo de Red Neuronal Profunda (MLP) y su generación de "re-                |    |

|       | giones lineales" por capa                                                     | 52 |

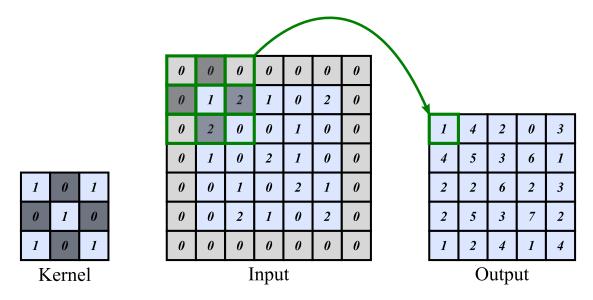

| 2.5.  | Ejemplo de convolución 2D, procesando un canal con $kernel$ de $3 \times 3$ , |    |

|       | stride 1, padding 1 y sin dilation                                            | 55 |

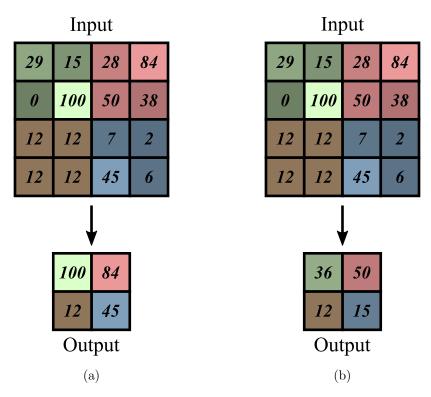

| 2.6.  | Ejemplos de <i>pooling</i> : a) MaxPool; b) AvgPool                           | 58 |

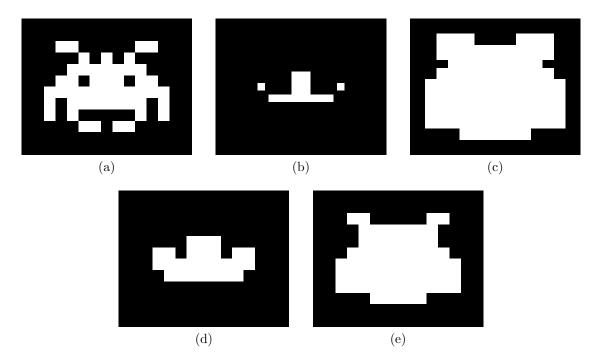

| 2.7.  | Ejemplos de operaciones morfológicas (binarias): a) imagen original;          |    |

|       | b) erosión; c) dilatación; d) apertura; e) cierre                             | 61 |

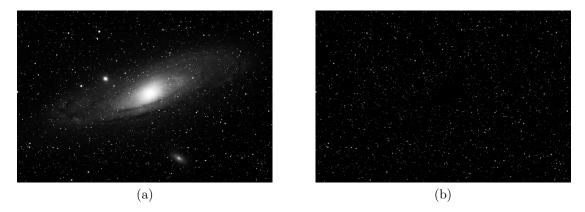

| 2.8.  | Operación Top-Hat aplicada a una imagen de ejemplo: a) imagen                 |    |

|       | original extraida de [1]; b) imagen procesada                                 | 62 |

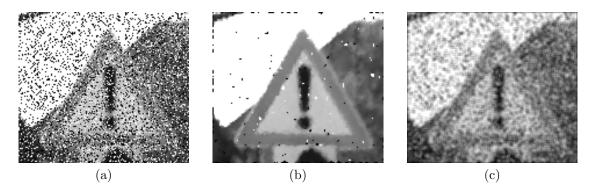

| 2.9.  | Reducción de ruido salt and pepper con operadores lineales y mor-             |    |

|       | fológicos: a) imagen original de [2], con ruido añadido; b) filtro de         |    |

|       | mediana; c) filtro AvgPool                                                    | 62 |

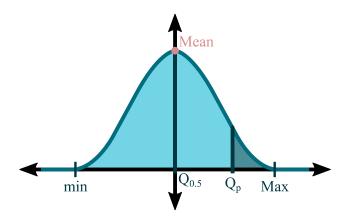

| 2.10. | Obtención del rango de datos a partir de su distribución                      | 64 |

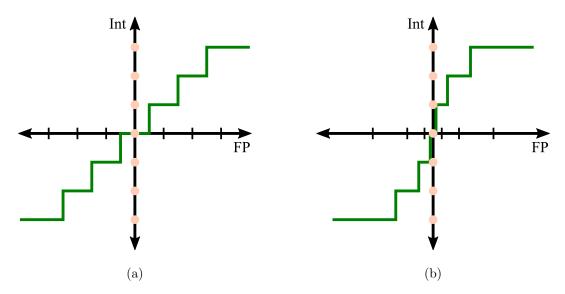

| 2.11. | Modelos de cuantización: a) Uniforme; b) No-Uniforme                          | 66 |

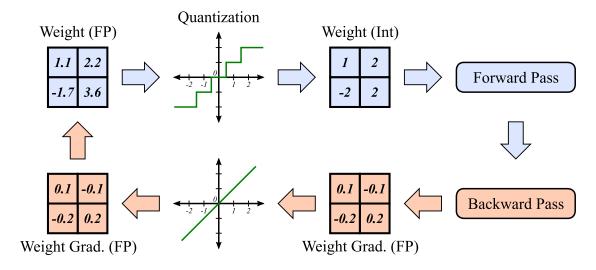

| 2.12. | Descripción gráfica del entrenamiento con cuantización (QAT)                  | 68 |

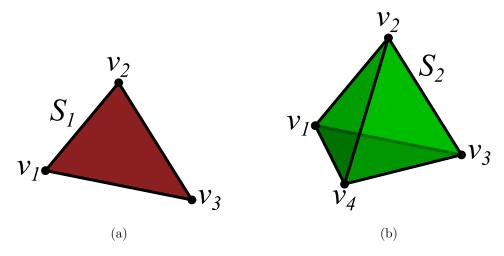

| 2.13. | Ilustración de símplices genéricos en: a) dos dimensiones (2D); b) tres       |    |

|       | dimensiones (3D)                                                              | 70 |

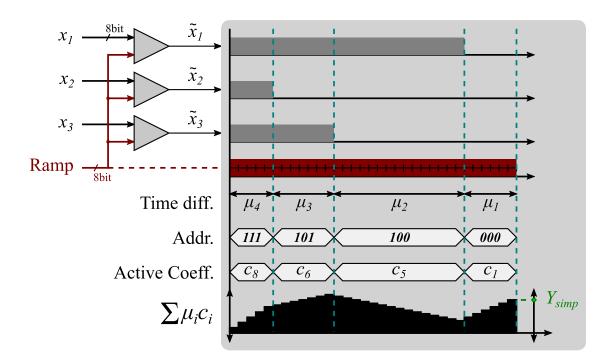

| 2.14. | Estructura de cómputo simplicial                                              | 72 |

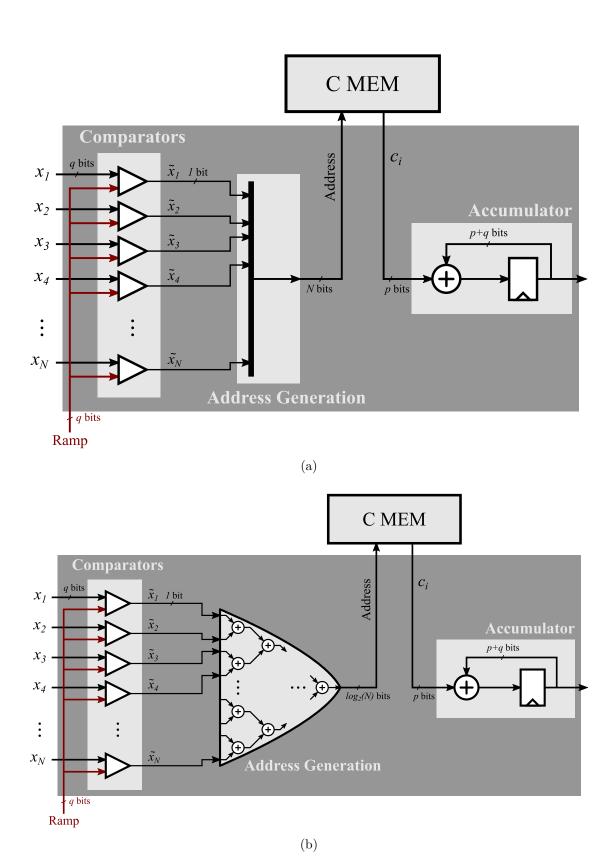

| 2.15. | Arquitecturas de procesamiento para funciones simpliciales: a) sim-           |    |

|       | plicial pura; b) simplicial simétrica                                         | 73 |

|       |                                                                               |    |

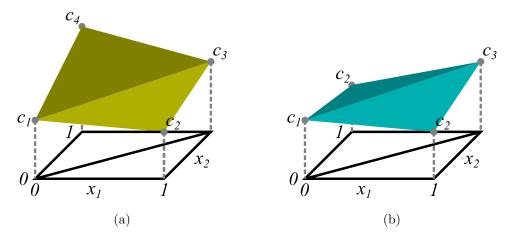

| 2.16. | Ejemplos de funciones simpliciales en dos dimensiones (dos entradas):                            |     |

|-------|--------------------------------------------------------------------------------------------------|-----|

|       | a) simplicial pura; b) simplicial simétrica                                                      | 74  |

| 3.1.  | Imágenes del dataset EuroSAT de [3,4]: a) SeaLake_1858; b) Forest_907.                           | 87  |

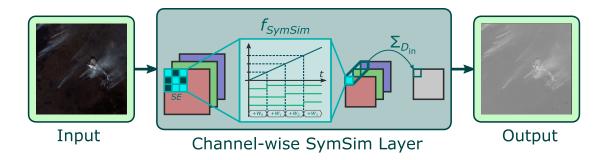

| 3.2.  | Ilustración de capa simplicial simétrica a canales separados ( ${\it ChSym}$ -                   |     |

|       | Sim)                                                                                             | 87  |

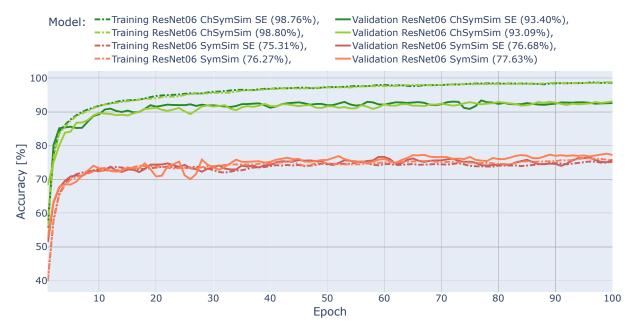

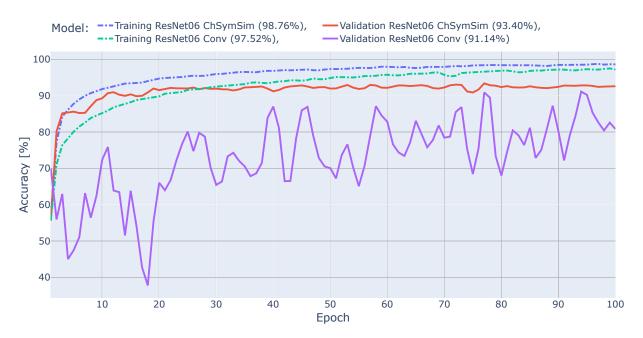

| 3.3.  | Comparación del desempeño para clasificar imágenes de EuroSAT                                    |     |

|       | ( $[3]$ y $[4]$ ) entre redes ResNet06 (Tabla D.4) con capas simpliciales                        |     |

|       | simétricas y Ch<br>SymSim, con y sin $SE$                                                        | 90  |

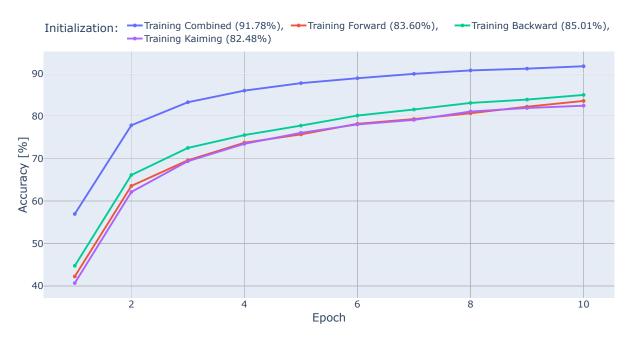

| 3.4.  | Primeras 10 épocas de entrenamiento de ChSymSim LeNet para cla-                                  |     |

|       | sificación del dataset FashionMNIST (Training), en base a diferen-                               |     |

|       | tes inicializaciones: Combined (producto $\gamma \hat{\gamma}$ ), Forward ( $\gamma$ ), Backward |     |

|       | $(\hat{\gamma})$ , Kaiming (normal) [5]                                                          | 96  |

| 3.5.  | Primeras 10 épocas de entrenamiento de ChSymSim ResNet06 (Ta-                                    |     |

|       | bla D.4) para clasificación del $dataset$ EuroSAT (Training), en base                            |     |

|       | a diferentes inicializaciones: Combined (producto $\gamma \hat{\gamma}$ ), Forward ( $\gamma$ ), |     |

|       | Backward $(\hat{\gamma})$ , Kaiming (normal) [5]                                                 | 97  |

| 3.6.  | Dataset GTSRB (German Traffic Sign Recognition Benchmark), pu-                                   |     |

|       | blicado en [2]                                                                                   | 98  |

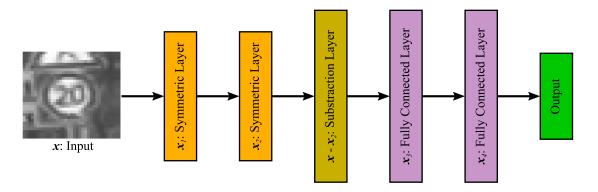

| 3.7.  | Residual Symmetric Simplicial Neural Network (RSSNN)                                             | 99  |

| 3.8.  | Resultado de entrenamientos de redes RSSNN y clasificación del $\it da$ -                        |     |

|       | taset GTSRB                                                                                      | 99  |

| 3.9.  | Deep Morphological Network (DMN) con primera capa utilizando                                     |     |

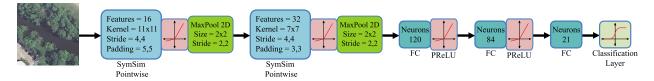

|       | algoritmo simplicial simétrico y convolución point-wise                                          | 101 |

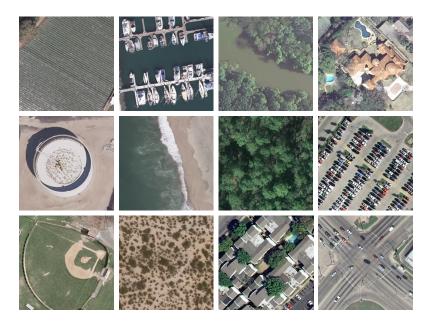

| 3.10. | UC Merced Land Use <i>Dataset</i> , publicado en [6]                                             | 102 |

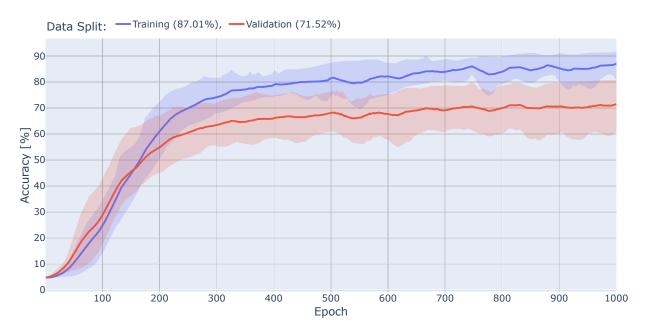

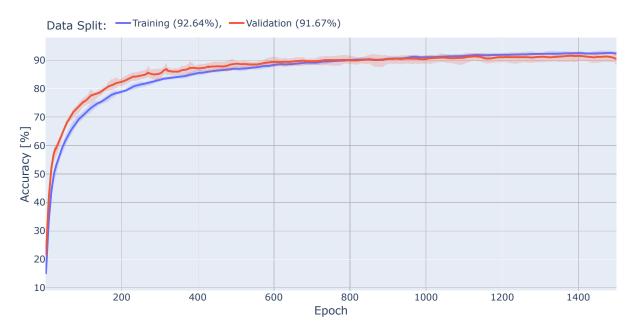

| 3.11. | Resultados del entrenamiento de red SymSim DMN utilizando $k\text{-}fold$                        |     |

|       | cross validation con el dataset UC Merced Land Use                                               | 103 |

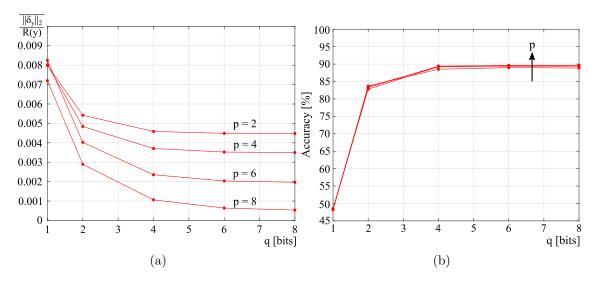

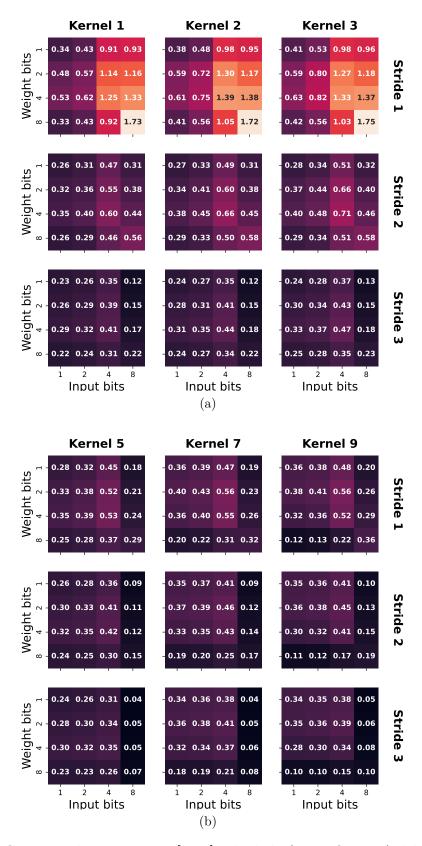

| 3.12. | a) Error numérico de la salida de la capa simplicial simétrica (Sym-                  |     |

|-------|---------------------------------------------------------------------------------------|-----|

|       | Sim) de la red DMN, en función de la cuantización de entradas y                       |     |

|       | pesos simpliciales; b) Clasificación de la red DMN para el dataset UC                 |     |

|       | Merced Land Use (training set) al cuantizar las entradas y pesos de                   |     |

|       | la capa SymSim de la red DMN. Para ambos gráficos $q$ representa los                  |     |

|       | bits de cuantización de las entradas y $p$ para los pesos                             | 04  |

| 3.13. | Deep Morphological Network (DMN), en su versión extendida, con                        |     |

|       | capas SymSim y convoluciones "point-wise"                                             | 04  |

| 3.14. | Resultados del entrenamiento de red SymSim DMN extendida, uti-                        |     |

|       | lizando capas de Batch<br>Norm y $k\text{-}fold\ cross\ validation\ con\ el\ dataset$ |     |

|       | UC Merced Land Use                                                                    | 05  |

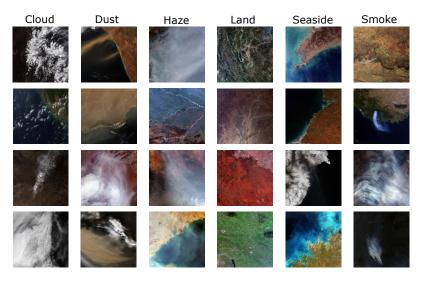

| 3.15. | . Dataset USTC SmokeRS, publicado en [7]                                              | .06 |

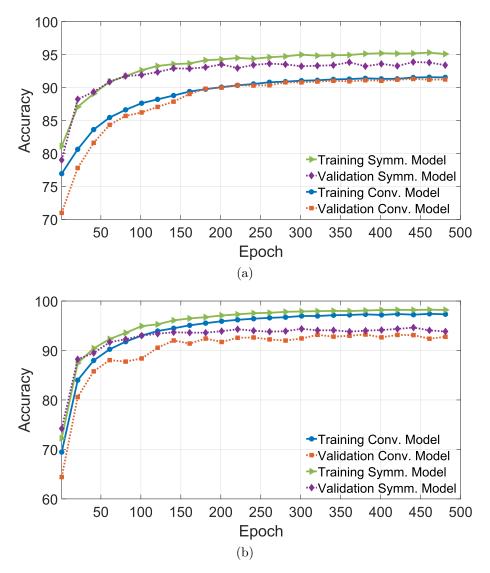

| 3.16. | a) Resultados de clasificación del dataset USTC SmokeRS con mode-                     |     |

|       | los ResNet04 ChSymSim y convolucional; b) Resultados de clasifica-                    |     |

|       | ción del dataset USTC SmokeRS con modelos ResNet06 ChSymSim                           |     |

|       | y convolucional. Resultados presentados en [8]                                        | .08 |

| 3.17. | . Dataset EuroSAT, publicado en [3,4]                                                 | 09  |

| 3.18. | Resultados del entrenamiento de modelos ResNet06 ChSymSim (Ta-                        |     |

|       | bla D.4) y convolucional para clasificación del dataset EuroSAT 1                     | 10  |

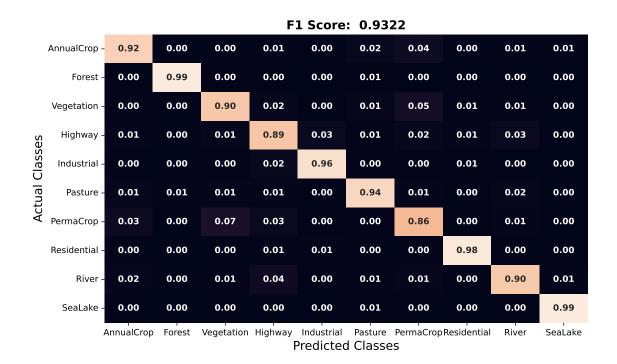

| 3.19. | Matriz de confusión del modelo ResNet06 cuantizado, clasificando                      |     |

|       | imágenes del dataset EuroSAT                                                          | 11  |

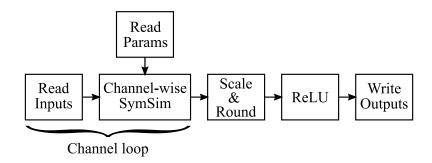

| 4.1.  | Descripción gráfica de la función ChSymSim, incluyendo operaciones                    |     |

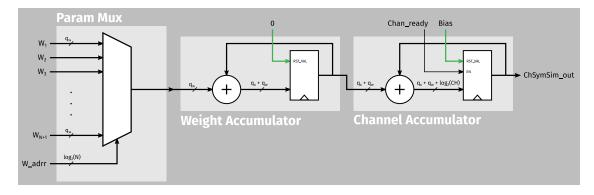

|       | auxiliares como carga de datos, escalado, ReLU y escritura de salidas. 1              | .15 |

| 4.2.  | Diagrama en bloques (alto nivel) propuesto para el operador ChSym-                    |     |

|       | Sim                                                                                   | 16  |

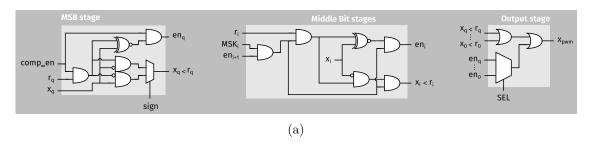

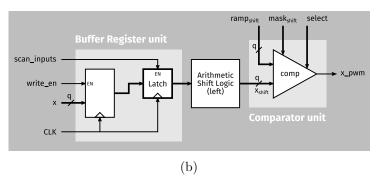

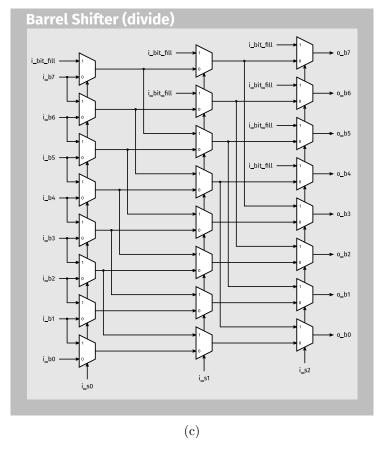

| 4.3.  | a) Circuito del comparador entre entrada $x$ y rampa $r$ , con salida                 |     |

|       | igual a $x\leqslant r;$ b) bloque de entrada y comparación del acelerador             |     |

|       | ChSymSim; c) barrel shifter para implementar un desplazamiento de                     |     |

|       | bits a la izquierda.                                                                  | 17  |

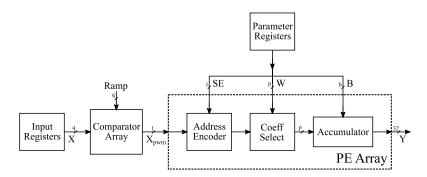

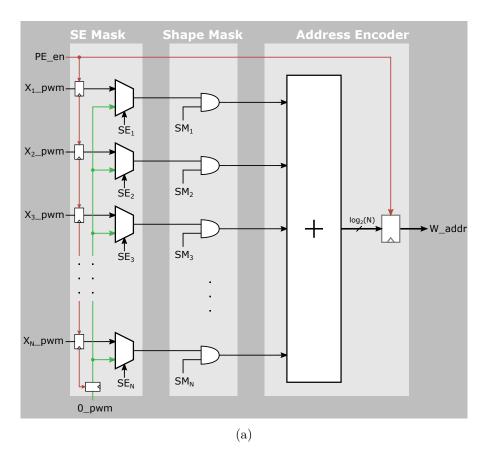

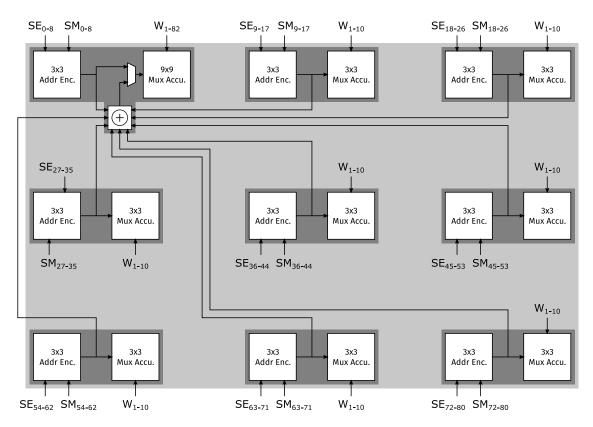

| 4.4.  | Elemento de procesamiento del acelerador ChSymSim: a) Bloque Ad-                          |     |

|-------|-------------------------------------------------------------------------------------------|-----|

|       | dress Encoder para generación (codificación) de la dirección de pesos;                    |     |

|       | b) Bloque Mux. Accumulator para selección de pesos y acumulación                          |     |

|       | de los mismos                                                                             | 119 |

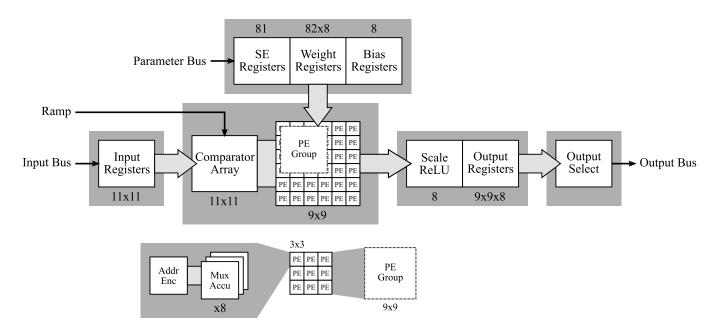

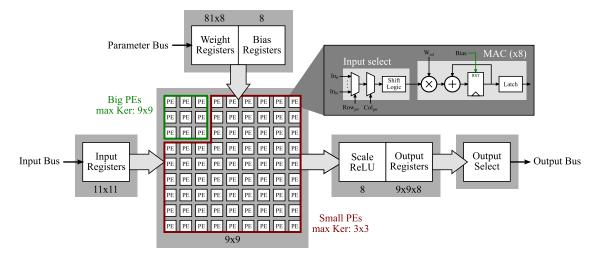

| 4.5.  | Diagrama en bloques del procesador ChSymSim                                               | 121 |

| 4.6.  | Agrupamiento de PEs (que no compartan entradas) para el cómputo                           |     |

|       | de kernels grandes en el acelerador ChSymSim                                              | 123 |

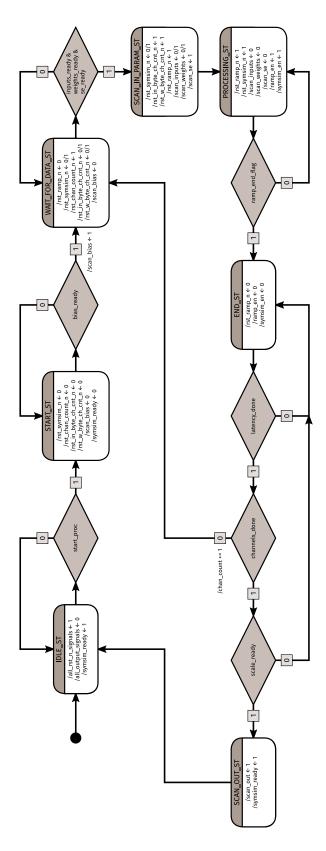

| 4.7.  | Diagrama de flujo para la máquina de estados (controlador) del ace-                       |     |

|       | lerador ChSymSim                                                                          | 125 |

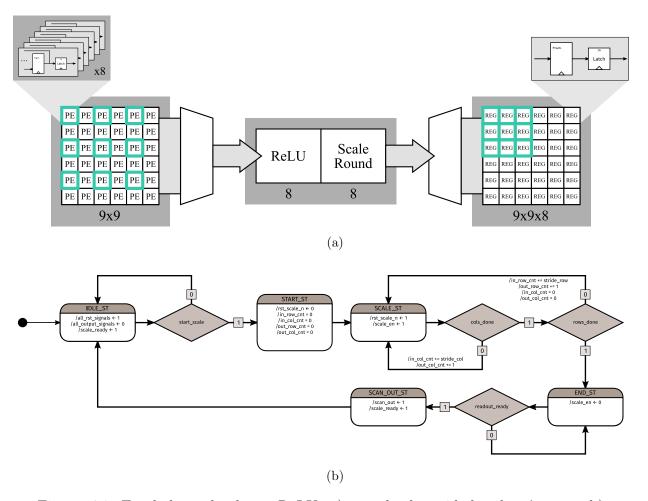

| 4.8.  | Escalado, redondeo y ReLU: a) arreglo de unidades de cómputo; b)                          |     |

|       | diagrama de estados del controlador.                                                      | 128 |

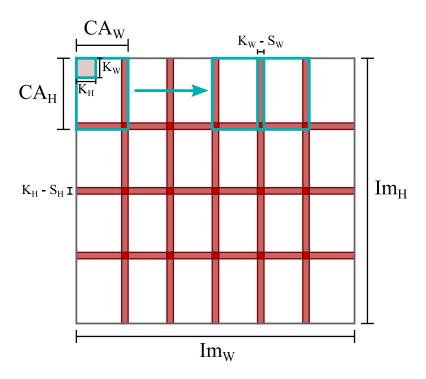

| 4.9.  | Regiones de solapamiento originadas por las entradas compartidas                          |     |

|       | entre series de procesamiento consecutivos, a partir de una imagen                        |     |

|       | o tensor de entrada de tamaño $Im_H \times Im_W,$ tomando porciones de                    |     |

|       | $CA_H \times CA_W$ en cada ciclo de procesamiento, con $kernel$ de tamaño                 |     |

|       | $k_H \times k_W$ y stride $(S_H, S_W)$                                                    | 131 |

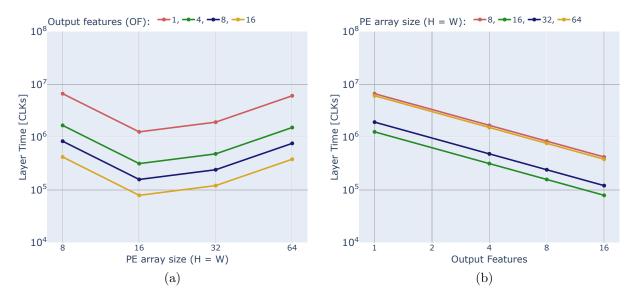

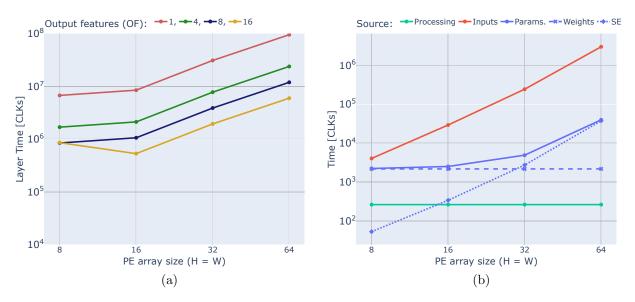

| 4.10. | Estimación de tiempo total para procesar la capa Layer $3_1$ de Res-                      |     |

|       | Net18 ChSymSim (Tabla D.1), al computar los 16 canales de entrada                         |     |

|       | en serie: a) Tiempo total vs. tamaño del arreglo de PEs; b) Tiempo                        |     |

|       | total vs. cantidad de features computados en paralelo                                     | 139 |

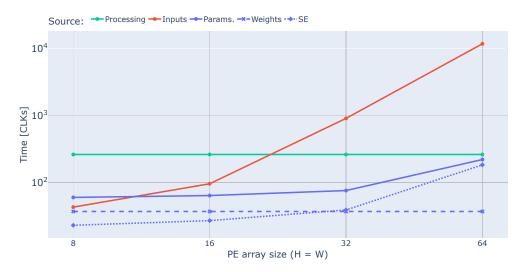

| 4.11. | Influencia en el tiempo total de la capa Layer<br>3 $_{1}$ de Res<br>Net<br>18 Ch<br>Sym- |     |

|       | Sim (Tabla D.1), por parte del procesamiento en sí mismo, carga de                        |     |

|       | entradas y escritura de parámetros, para 8 features de salida                             | 140 |

| 4.12. | Estimación de tiempos para procesar la capa Layer $3_1$ de ResNet18                       |     |

|       | ChSymSim (Tabla D.1), al computar los 16 canales de entrada en                            |     |

|       | paralelo: a) tiempo total; b) tiempos de cómputo de PEs, carga de                         |     |

|       | entradas y escritura de parámetros                                                        | 141 |

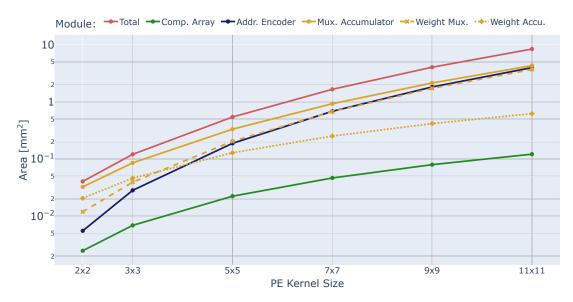

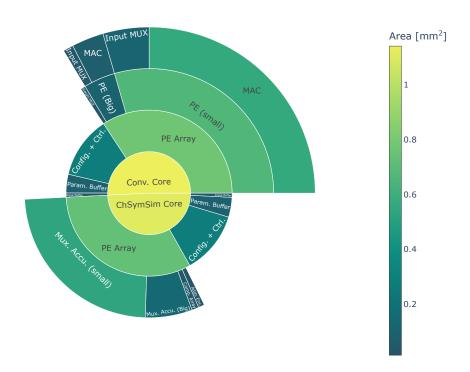

| 4.13. | Área del operador Ch<br>SymSim y sus módulos, en función del tamaño                       |     |

|       | del kernel, para un solo grupo de PEs y 8 features de salida con                          |     |

|       | diferente $SE$ para cada uno                                                              | 143 |

| 4.14. | Área del core Ch<br>SymSim y sus módulos, en función del tamaño del                       |     |

|       | kernel, para un solo grupo de PEs y 8 features de salida                                  | 144 |

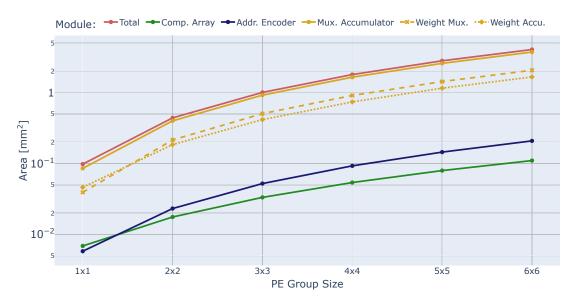

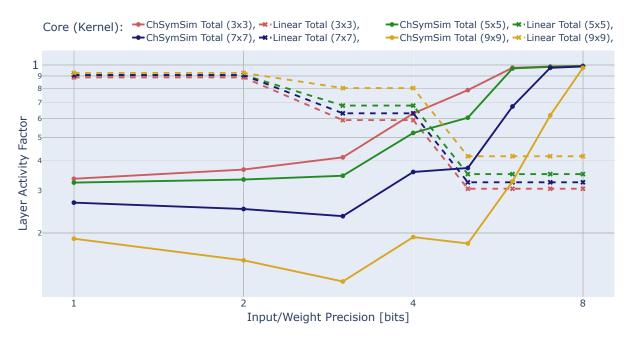

| 4.15. Area del core ChSymSim y sus módulos, en función del tamaño de          |

|-------------------------------------------------------------------------------|

| grupo de PEs, con kernel de tamaño $3\times 3$ y 8 features de salida por     |

| PE                                                                            |

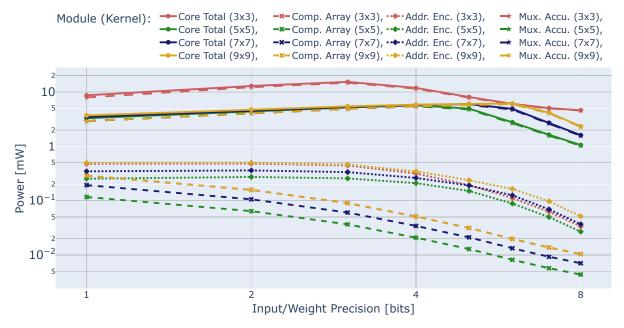

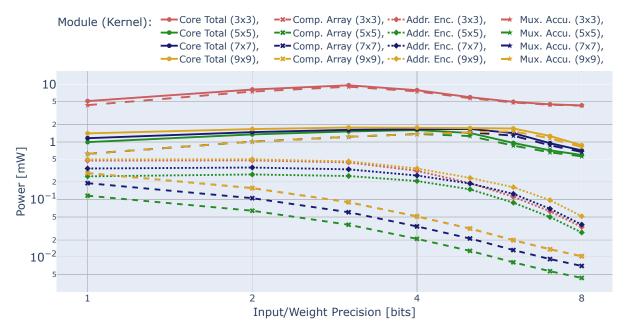

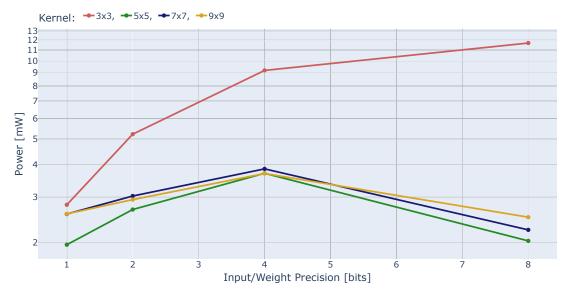

| 4.16. Consumo de potencia del operador ChSymSim y sus módulos, en             |

| función del tamaño del kernel y la precisión                                  |

| 4.17. Consumo de potencia del operador ChSymSim y sus módulos, en             |

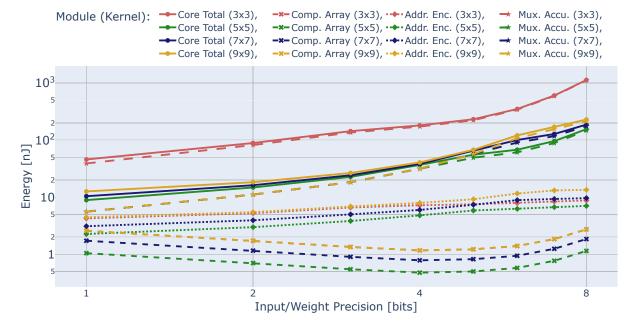

| función del tamaño del kernel y la precisión, utilizando multiplexores        |

| optimizados (entradas reordenadas)                                            |

| 4.18. Consumo energético del operador ChSymSim y sus módulos, en fun-         |

| ción del tamaño del kernel y la precisión, utilizando multiplexores           |

| optimizados (entradas reordenadas)                                            |

| 4.19. Diagrama en bloques del operador convolucional                          |

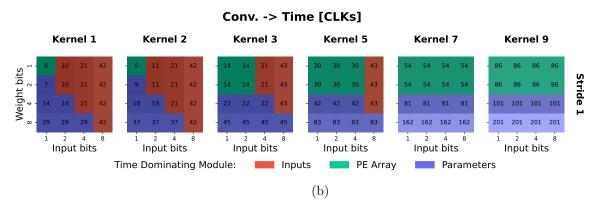

| 4.20. Tiempos de procesamiento de un canal de entrada, considerando carga     |

| de entradas y parámetros en $pipeline$ con $buses$ de 64 bits, ignorando      |

| carga inicial para: a) acelerador ChSymSim; b) operador convolucional.153     |

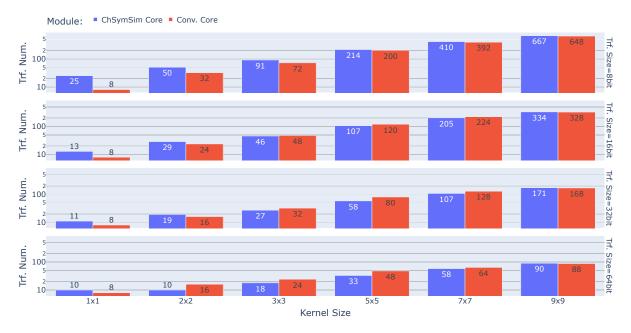

| 4.21. Número de transacciones para la carga de parámetros, requeridas por     |

| los procesadores convolucional y ChSymSim                                     |

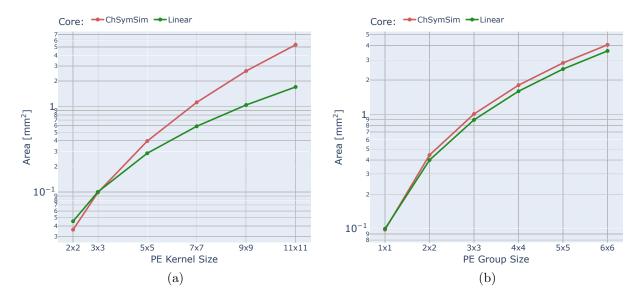

| 4.22. Comparación de área entre operadores ChSymSim y convolucional,          |

| con 8 features de salida por PE: a) en función de la cantidad del             |

| tamaño de kernel por PE, para un solo grupo de PEs; b) en función             |

| del tamaño de grupo de PEs, con tamaño de $kernel$ por PE de $3\times3$ . 156 |

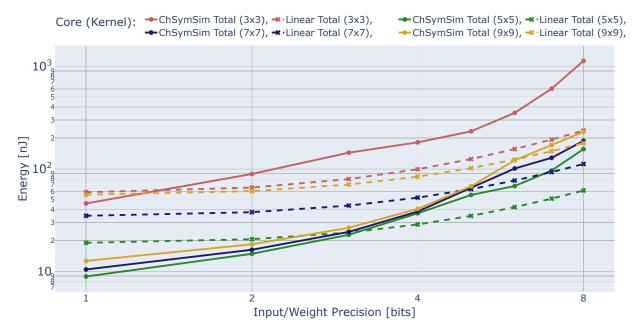

| 4.23. Energía estimada para los aceleradores ChSymSim y convolucional,        |

| en función de la precisión de las entradas. Procesadores con tamaño           |

| de $kernel$ mínimo de 3 × 3, grupos de PE de 3 × 3 y 8 features de            |

| salida en paralelo                                                            |

| 4.24. Comparación de área (post-síntesis) de los operadores ChSymSim y        |

| convolucional, junto a todos los módulos que los componen                     |

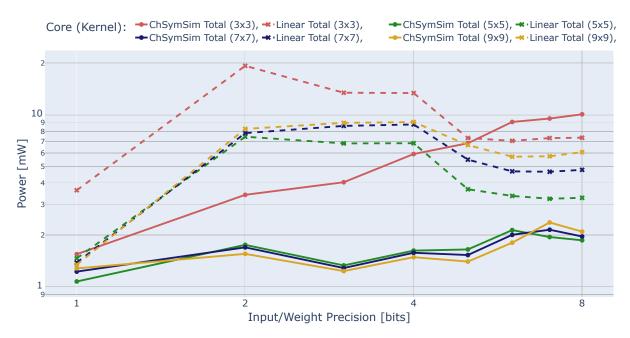

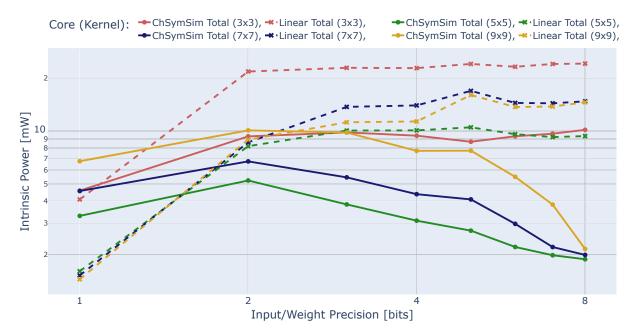

| 4.25. Resultados de consumo de potencia total en los aceleradores ChSym-      |

| Sim y convolucional (lineal), extraídos de la actividad ("switching           |

| activity") de simulaciones post-síntesis ideales                              |

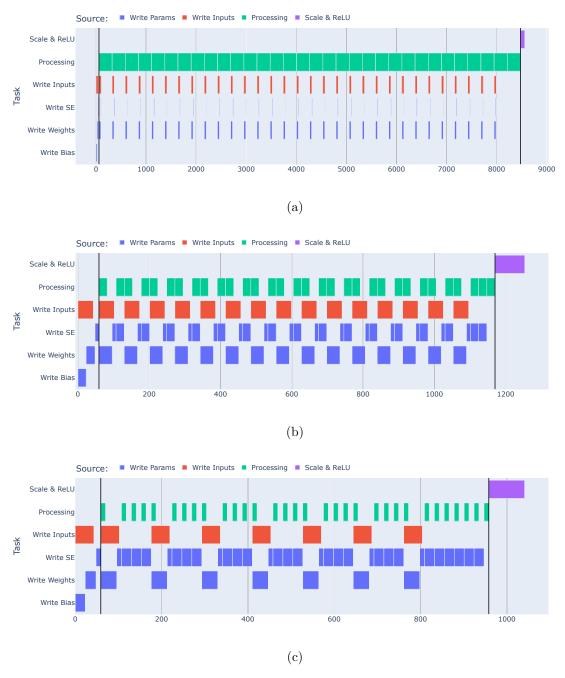

| 4.26.      | Tiempo de cómputo total (incluyendo carga de datos con DMA) para                    |           |

|------------|-------------------------------------------------------------------------------------|-----------|

|            | el operador Ch<br>SymSim con $kernel$ 3 × 3, 32 canales, 8 $features$ de            |           |

|            | salida y precisión de entrada/pesos de: a) 8 bits; b) 4 bits; c) 2 bits             | 162       |

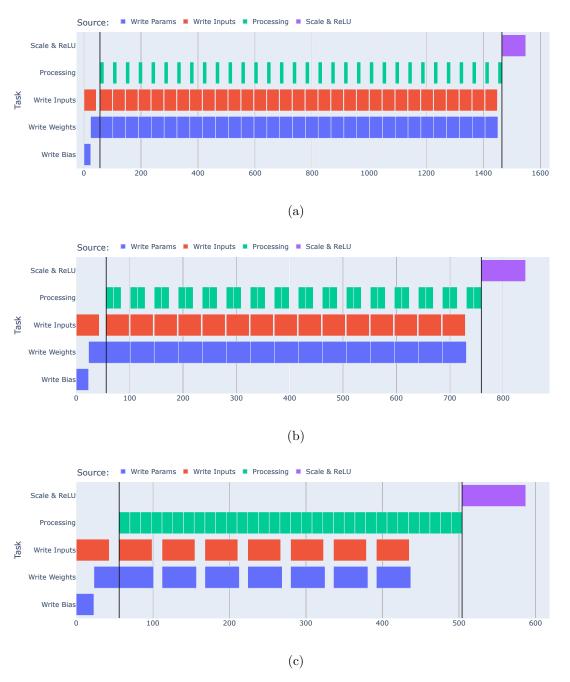

| 4.27.      | Tiempo de cómputo total (incluyendo carga de datos con DMA) para                    |           |

|            | el acelerador convolucional con $kernel~3\times3,~32$ canales, 8 "features"         |           |

|            | de salida y precisión de entrada/pesos de: a) 8 bits; b) 4 bits; c) 2 bits          | .164      |

| 4.28.      | Actividad total de los aceleradores ChSymSim y convolucional, cal-                  |           |

|            | culada a partir de los ciclos de procesamiento y espera de datos (con               |           |

|            | 32 canales de entrada)                                                              | 165       |

| 4.29.      | Resultados de consumo de potencia intrínseca (ignorando carga de                    |           |

|            | datos y tiempos de espera) de los procesadores ChSymSim y convo-                    |           |

|            | lucional (simulaciones post-síntesis ideales).                                      | 166       |

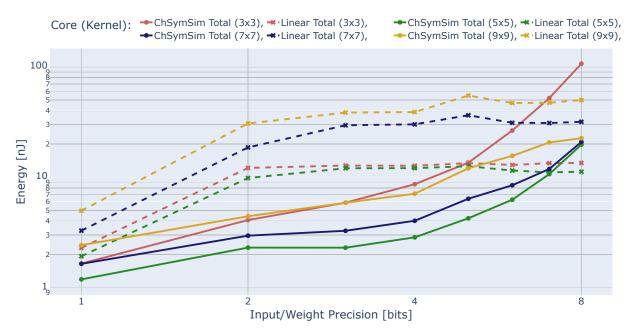

| 4.30.      | Resultados de energía de los aceleradores ChSymSim y convolucio-                    |           |

|            | nal, a partir del consumo de potencia total (simulaciones post-síntesis             |           |

|            | ideales) y tiempo de cómputo incluyendo ciclos de espera                            | 167       |

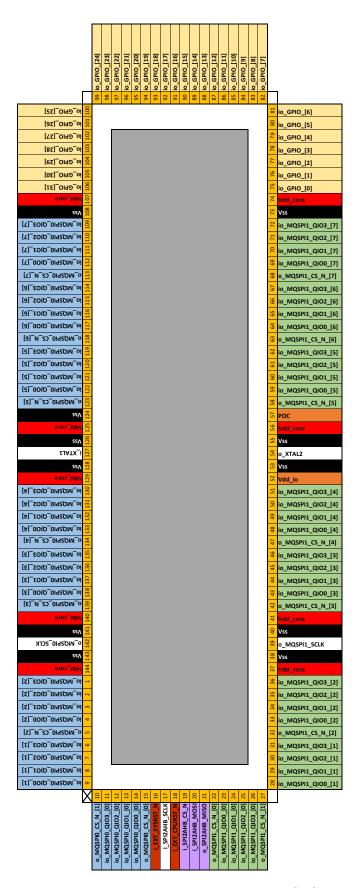

| F 1        | Disir annual VI CaC I annual annual ach and a lair falaire de                       |           |

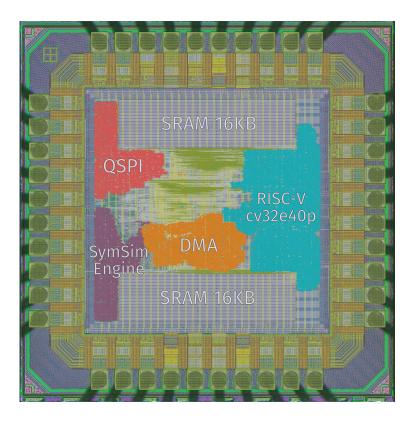

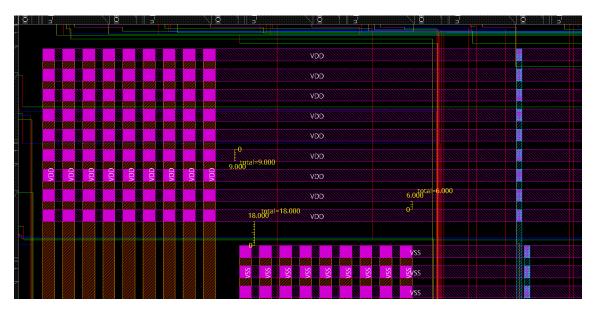

| 5.1.       | DigineuronV1 SoC, layout superpuesto sobre el chip fabricado, mar-                  | 170       |

| ۲.0        | cando los bloques más importantes del mismo                                         |           |

| 5.2.       | Diagrama en bloques con los módulos de DigineuronV1 SoC                             | 173       |

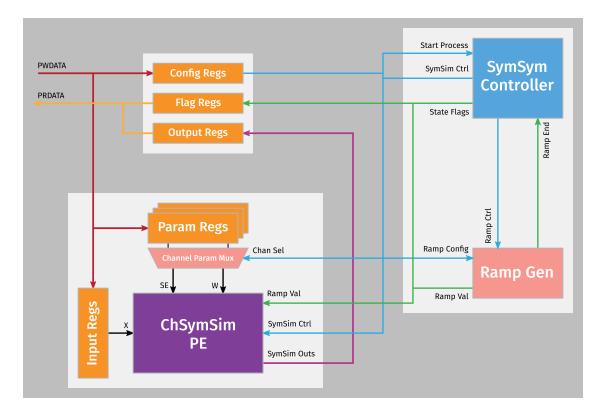

| 5.3.       | Diagrama en bloques del acelerador ChSymSim implementado en Di-                     | 1 7 4     |

| - 1        | gineuronV1                                                                          | 174       |

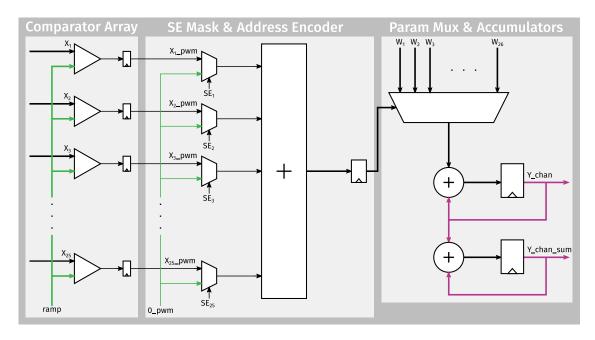

| 5.4.       | Diagrama en bloques del PE perteneciente al operador ChSymSim                       | 1 <b></b> |

|            | implementado en DigineuronV1                                                        | 175       |

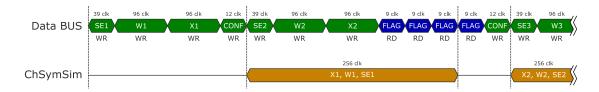

| 5.5.       | Pipeline de procesamiento del acelerador ChSymSim integrado en Di-                  | 1 70      |

| <b>-</b> a | gineuronV1                                                                          | 176       |

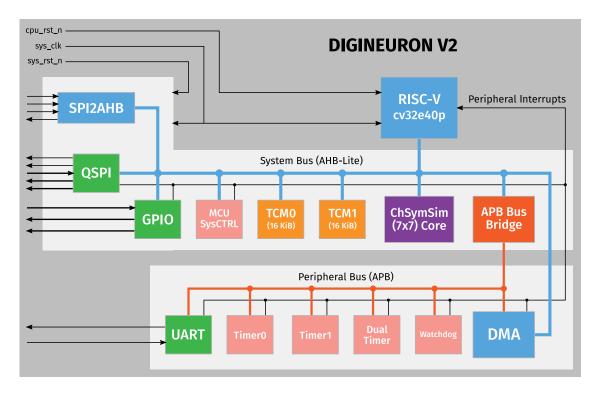

| 5.6.       | DigineuronV2 SoC, layout superpuesto sobre el die, marcando los                     | 4=0       |

|            | bloques más importantes del mismo.                                                  |           |

| 5.7.       | Diagrama en bloques con los módulos de DigineuronV2 SoC                             | 179       |

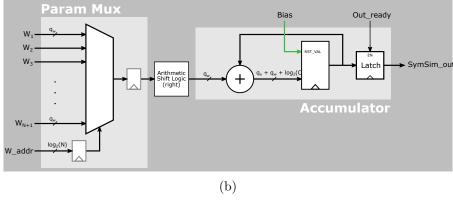

| 5.8.       | Sub-bloque Mux. Accumulator del PE en el acelerador ChSymSim                        |           |

|            | fabricado en DigineuronV2                                                           | 180       |

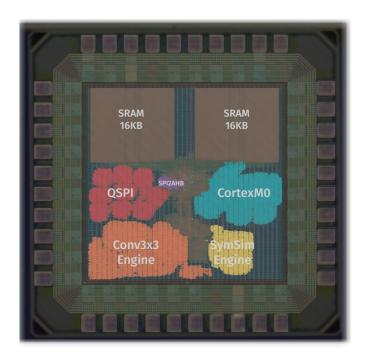

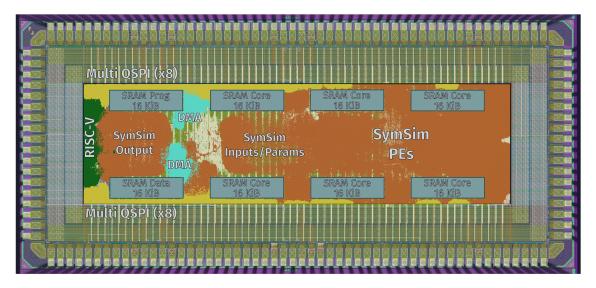

| 5.9.       | Digineuron V3a SoC, <i>layout</i> superpuesto sobre el <i>die</i> , donde se marcan |           |

|            | los bloques más importantes del mismo                                               | 182       |

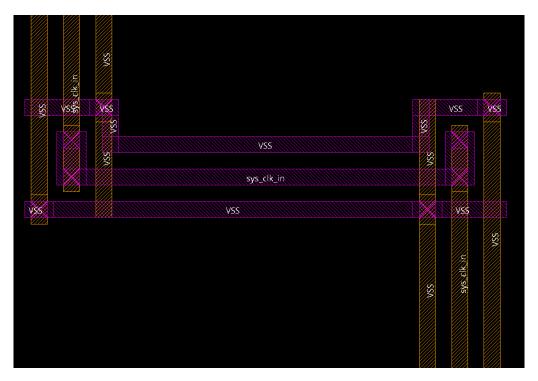

| 5.10. | Anillo de metales para distribución de potencia en el SoC Digineu-                                     |     |

|-------|--------------------------------------------------------------------------------------------------------|-----|

|       | ronV3a                                                                                                 | .83 |

| 5.11. | Línea de distribución de la señal de reloj (de pads a core)                                            | 84  |

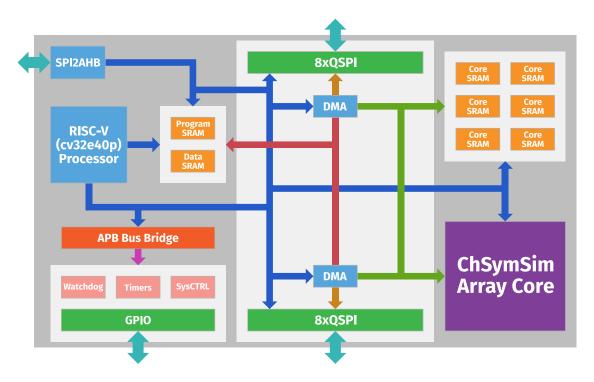

| 5.12. | Diagrama en bloques con los módulos de Digineuron<br>V3a SoC.     .                                    | 86  |

| 5.13. | Diagrama en bloques con el acelerador ChSymSim y las interfaces con                                    |     |

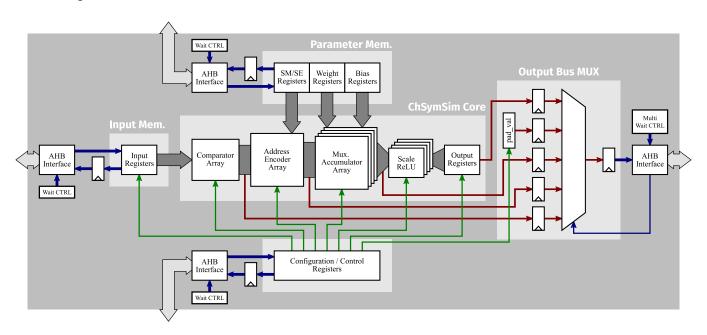

|       | el <i>bus</i> AHB                                                                                      | 91  |

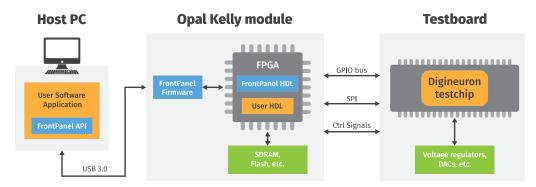

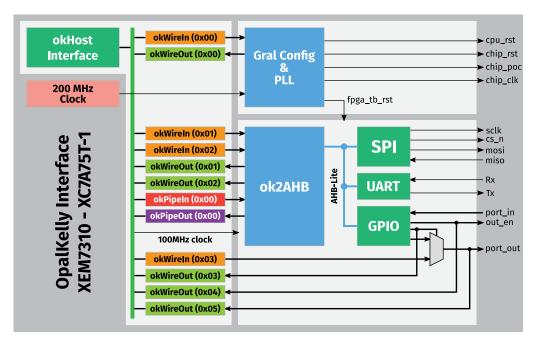

| 5.14. | Entorno de pruebas para la evaluación de los SoCs fabricados 1                                         | 94  |

| 5.15. | Diagrama de bloques de la plataforma de pruebas (testbech) en FPGA.1                                   | 94  |

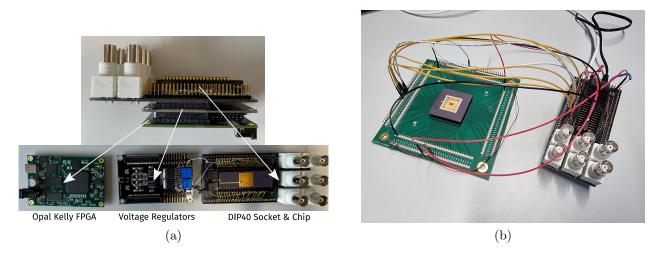

| 5.16. | Plataformas de evaluación para los SoC: a) DigineuronV1 y V2; b)                                       |     |

|       | DigineuronV3a                                                                                          | 95  |

| 5.17. | Patrón de datos escrito y leído del <i>chip</i> , por medio de la interfaz                             |     |

|       | SPI2AHB, como prueba de "vida" del sistema                                                             | 96  |

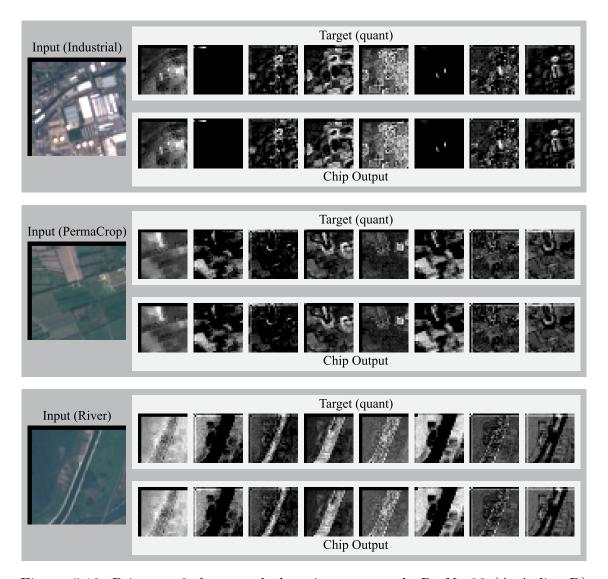

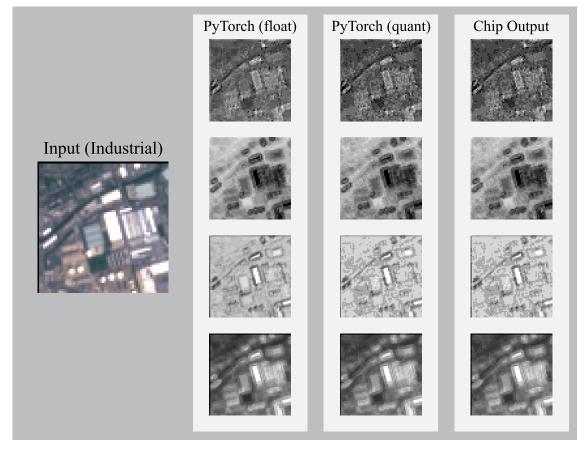

| 5.18. | Primeros 8 features de la primera capa de ResNet06 (Apéndice D)                                        |     |

|       | obtenidas por el acelerador ChSymSim integrado en DigineuronV3a 1                                      | 98  |

| 5.19. | Features del segundo filtro de capa 2 en ResNet06 (Apéndice D),                                        |     |

|       | con imagen de entrada de EuroSat [3,4], procesada con el acelerador                                    |     |

|       | ChSymSim de DigineuronV3a                                                                              | .99 |

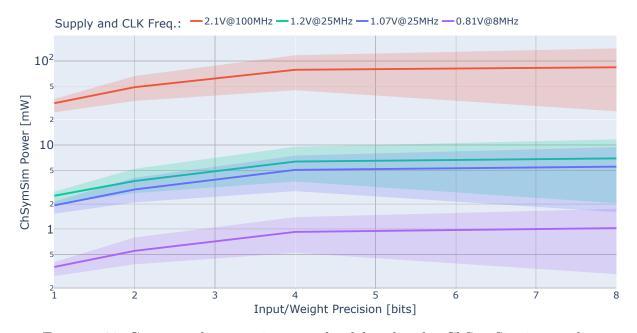

| 5.20. | Consumo de potencia promedio del acelerador ChSymSim integrado                                         |     |

|       | en Digineuron<br>V3a, con <i>stride</i> 1 y diversos tamaños de <i>kernel</i> 2                        | 05  |

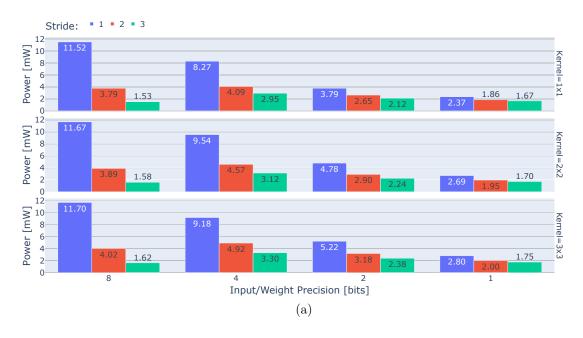

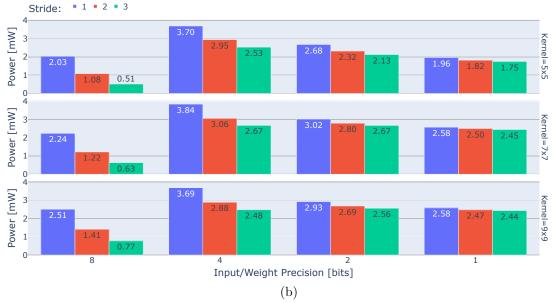

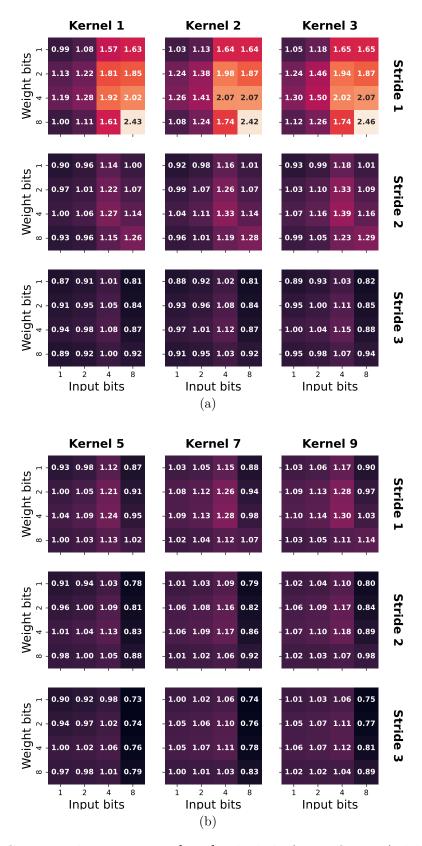

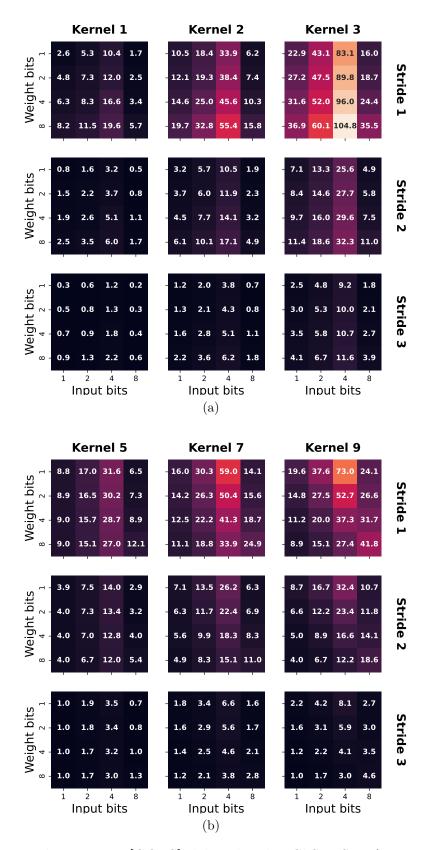

| 5.21. | Consumo de potencia del acelerador ChSymSim integrado en Digi-                                         |     |

|       | neuronV3a, para tensión/frecuencia nominales de 1,2V@25MHz, con                                        |     |

|       | diversos valores de stride y kernel: a) $1 \times 1$ a $3 \times 3$ ; b) $5 \times 5$ a $9 \times 9$ . | 207 |

| 5.22. | Consumo de potencia del acelerador ChSymSim integrado en Digineu-                                      |     |

|       | ron<br>V3a, para tensión/frecuencia nominales de 1,2<br>V@25MHz y $stride$                             |     |

|       | 1                                                                                                      | 208 |

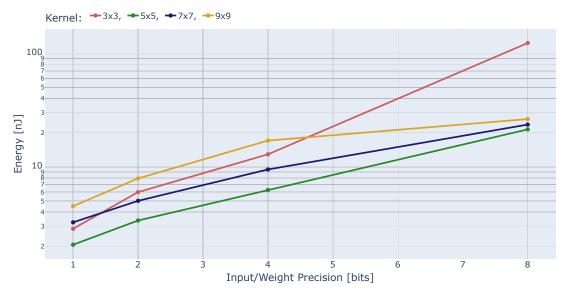

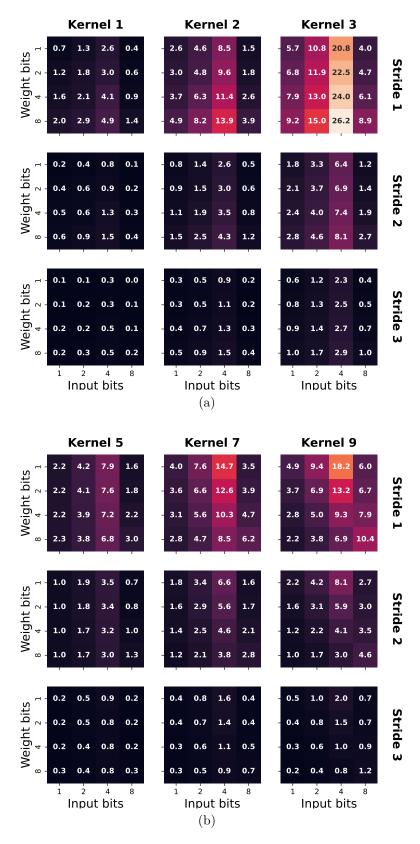

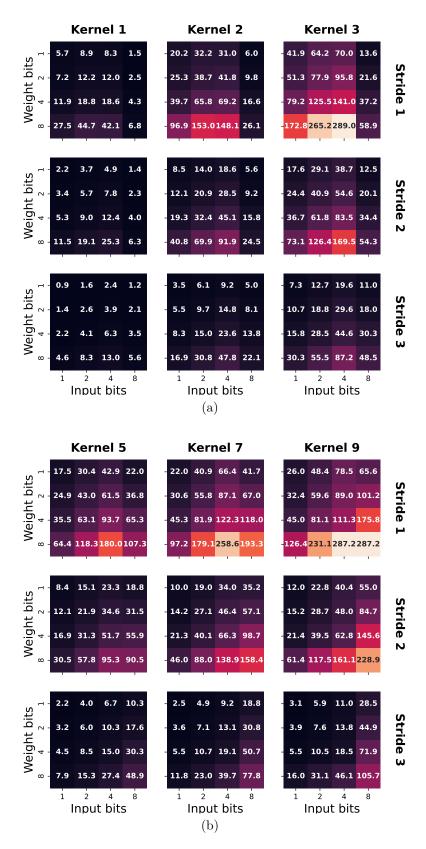

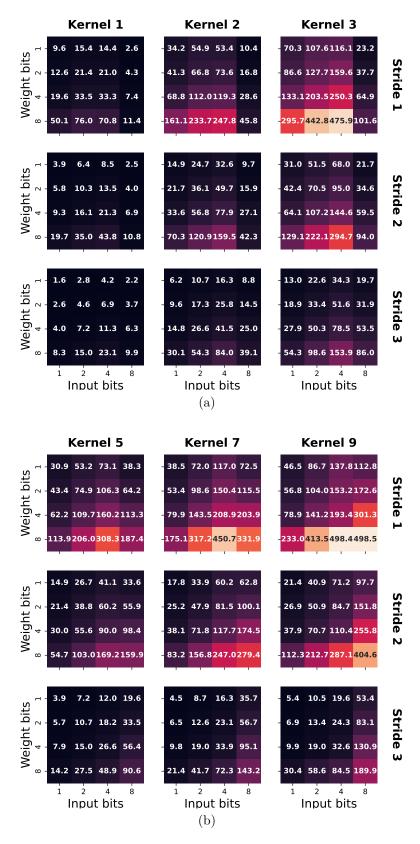

| 5.23. | Consumo energético del acelerador ChSymSim integrado en Digineu-                                       |     |

|       | ron<br>V3a, para tensión/frecuencia nominales de 1,2<br>V@25MHz y $stride$                             |     |

|       | 1                                                                                                      | 209 |

| D 1   |                                                                                                        |     |

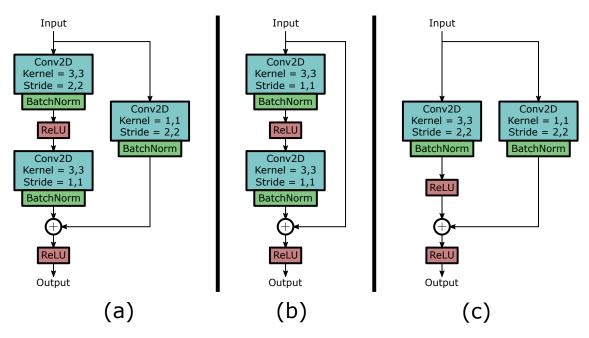

| D.1.  | Bloques básicos (Basic Blocks) de las arquitecturas ResNet: a) Bloque                                  |     |

|       | básico con down-sample; b) Bloque Básico; c) Bloque Básico reducido                                    |     |

|       | y con down-sample                                                                                      | 240 |

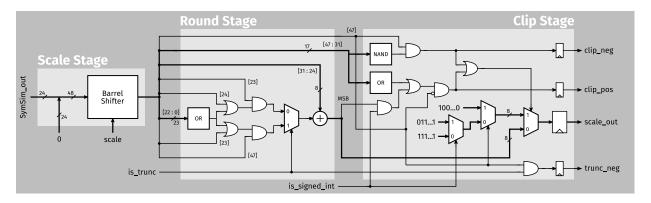

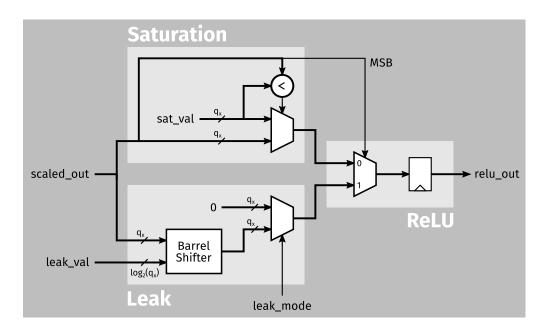

| E.1. | Diseño de la unidad en <i>hardware</i> para escalado y redondeo 2                           | :54 |

|------|---------------------------------------------------------------------------------------------|-----|

| E.2. | Arquitectura en <i>hardware</i> para el cómputo de activaciones ReLU 2                      | !55 |

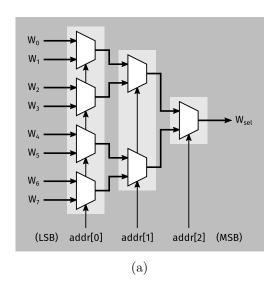

| F.1. | Selectores de pesos: a) Selector tradicional (entradas ordenadas); b)                       |     |

|      | Selector optimizado para lecturas con dirección en incrementos 2                            | 258 |

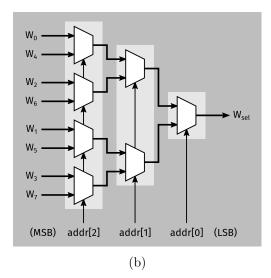

| F.2. | Selector de pesos <i>One-Hot</i> , separado en codificación de dirección y                  |     |

|      | selector propiamente dicho (compuertas AND y OR)                                            | 261 |

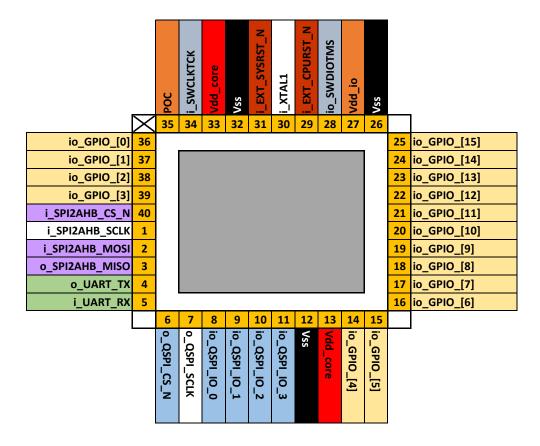

| G.1. | Ubicación de las señales en el SoC Digineuron<br>V1: esquema de $\it pads$ 2                | 263 |

| G.2. | Ubicación de las señales en el SoC DigineuronV1: diagrama de encap-                         |     |

|      | sulado DIL40                                                                                | 264 |

| G.3. | Ubicación de las señales en el SoC DigineuronV2: diagrama de encap-                         |     |

|      | sulado DIL40                                                                                | 264 |

| G.4. | Ubicación de las señales en el SoC Digineuron<br>V2: esquema de $\it pads.$ . 2             | 265 |

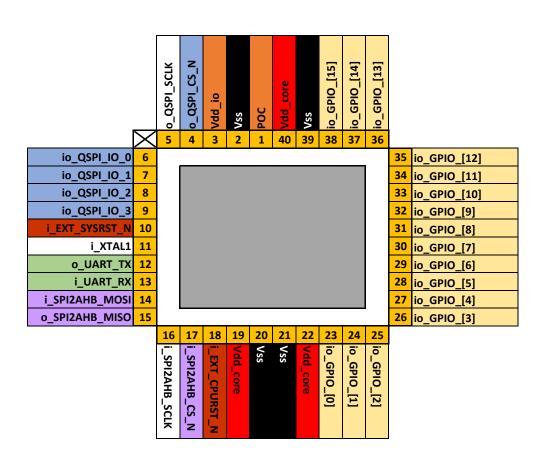

| G.5. | Ubicación de las señales en los $pads$ del SoC Digineuron<br>V3a 2                          | 266 |

| G.6. | Ubicación de las señales en los $pins$ de Digineuron<br>V3a, con encapsu-                   |     |

|      | lado CPGA144                                                                                | :67 |

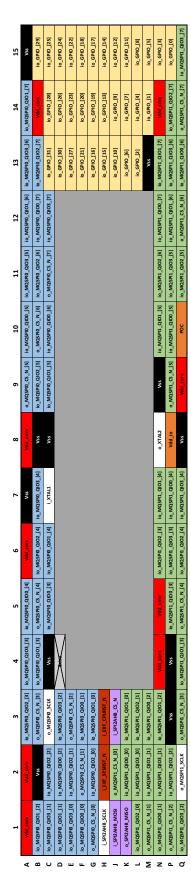

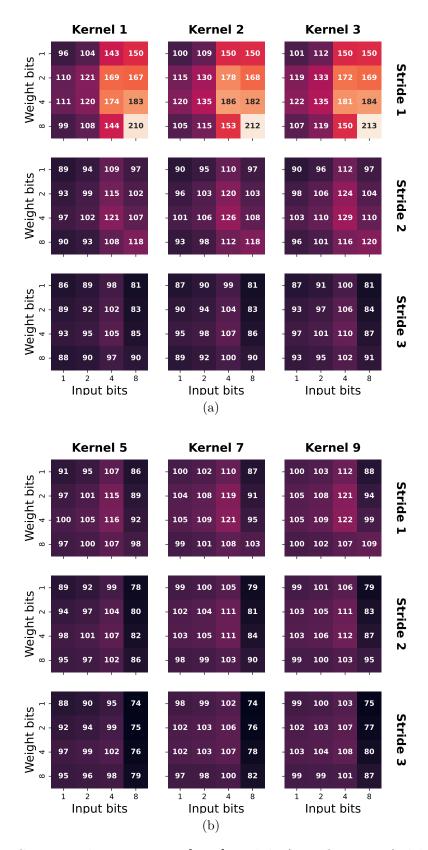

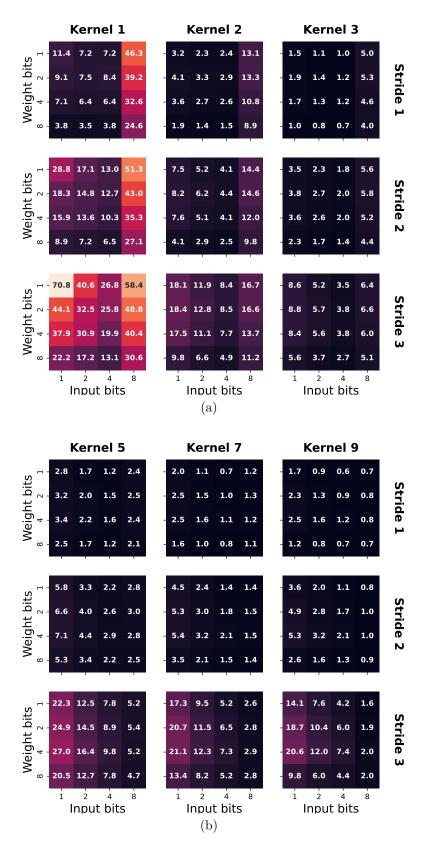

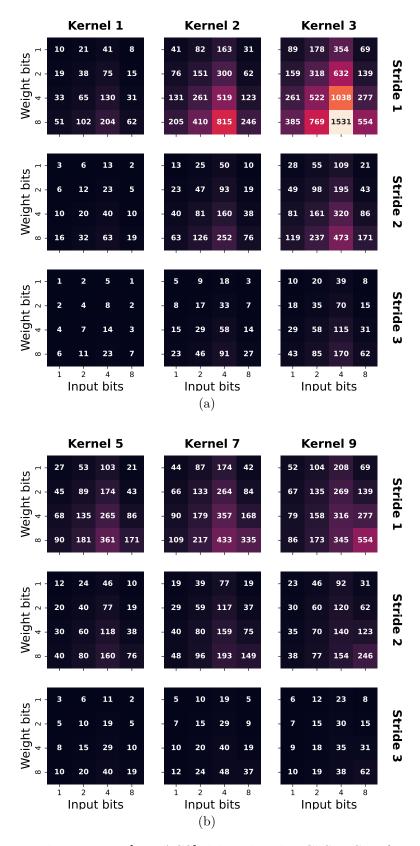

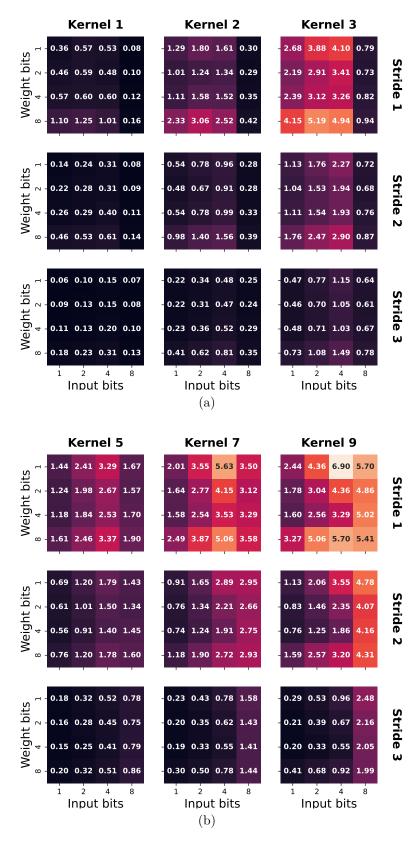

| J.1. | Consumo de potencia en $[\mathrm{mW}]$ medido (1,2V@25MHz) del SoC Digi-                    |     |

|      | neuron<br>V3a, realizando solo transferencias de datos ( $mu$ P y DMAs),                    |     |

|      | con diferentes configuraciones de Ch<br>SymSim: a) kernel pequeños (1×1                     |     |

|      | hasta $3 \times 3$ ; b) kernel grandes (hasta $9 \times 9$ )                                | 289 |

| J.2. | Consumo de potencia en $[\mathrm{mW}]$ medido (1,2V@25MHz) del SoC Digi-                    |     |

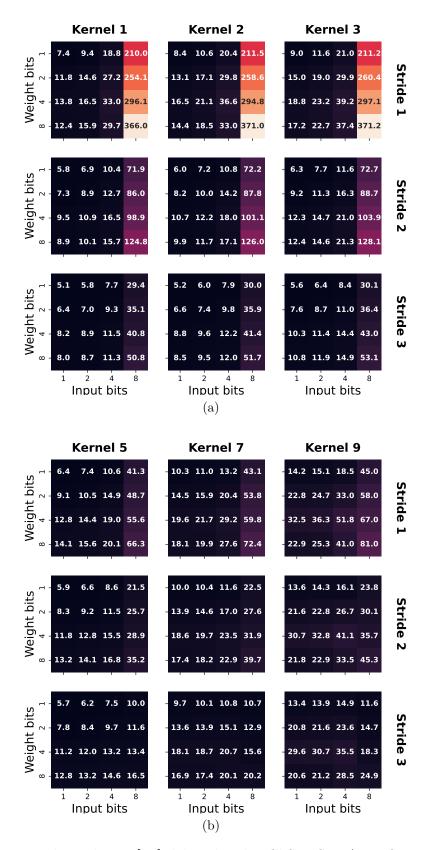

|      | neuronV3a, ejecutando diferentes configuraciones de ChSymSim: a)                            |     |

|      | kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 2                      | 290 |

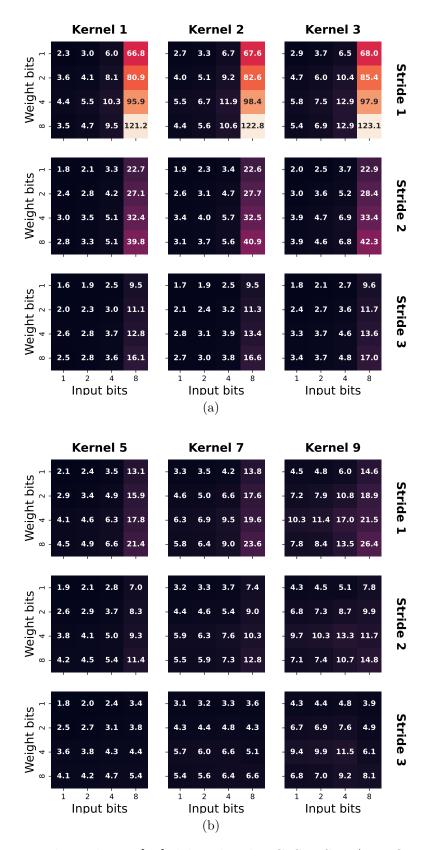

| J.3. | Consumo de potencia en $[\mathrm{mW}]$ calculado (1,2V@25MHz) del acele-                    |     |

|      | rador ChSymSim en DigineuronV3a, ejecutando diferentes configura-                           |     |

|      | ciones: a) kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta                    |     |

|      | $9 \times 9$ )                                                                              | 291 |

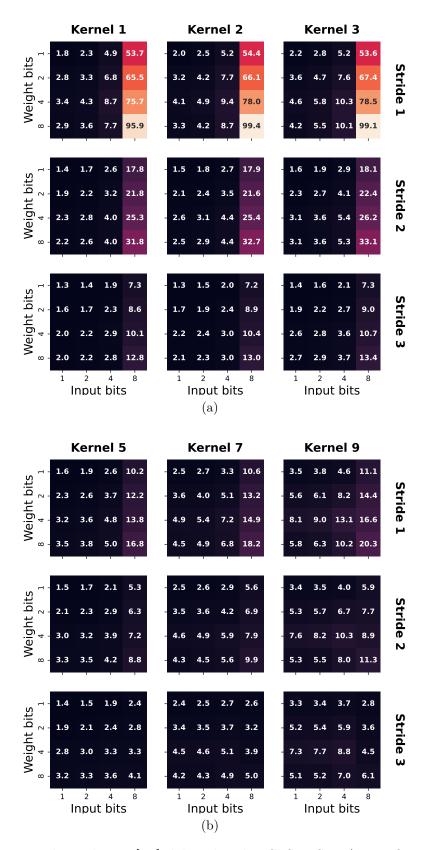

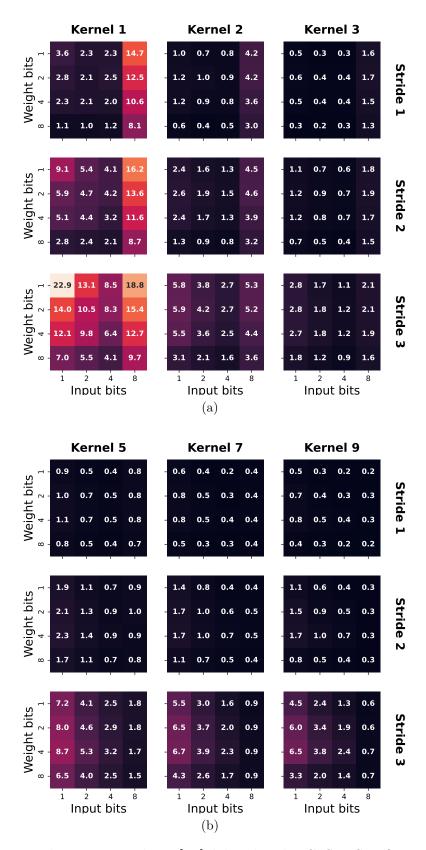

| J.4. | Consumo de potencia en $[\mathrm{mW}]$ medido (1,07<br>V@25MHz) del So<br>C Di-             |     |

|      | gineuronV3a, ejecutando diferentes configuraciones de ChSymSim: a)                          |     |

|      | kernel pequeños (1 $\times$ 1 hasta 3 $\times$ 3); b) kernel grandes (hasta 9 $\times$ 9) 2 | 92  |

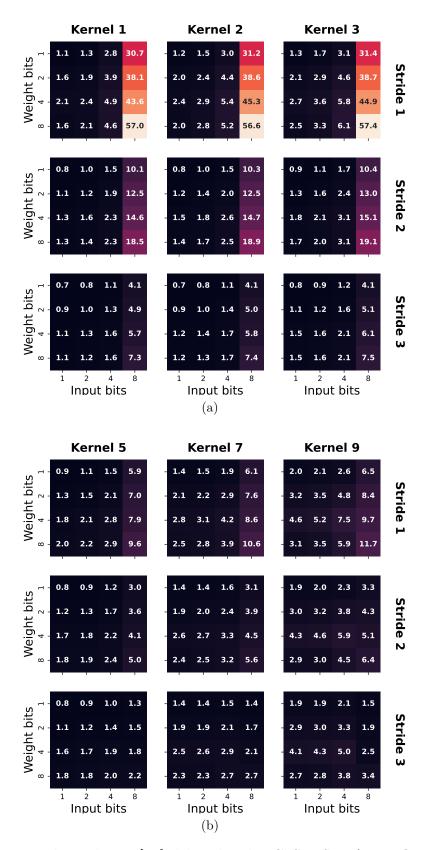

| J.5.  | Consumo de potencia en [mW] calculado (0,81V@8MHz) del SoC                         |       |

|-------|------------------------------------------------------------------------------------|-------|

|       | DigineuronV3a, ejecutando diferentes configuraciones: a) kernel pe-                |       |

|       | queños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9)                        | . 293 |

| J.6.  | Consumo de potencia en $[\mathrm{mW}]$ medido (1,07<br>V@25MHz) del SoC Di-        |       |

|       | gineuron<br>V3a, realizando solo transferencias de datos (<br>$mu{\rm P}$ y DMAs), |       |

|       | con diferentes configuraciones de Ch<br>SymSim: a) kernel pequeños (1×1            |       |

|       | hasta $3 \times 3$ ; b) kernel grandes (hasta $9 \times 9$ )                       | . 294 |

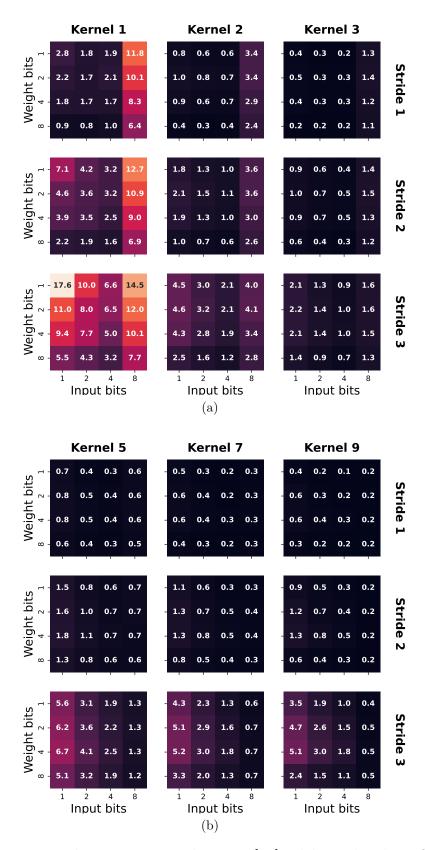

| J.7.  | Consumo de potencia en $[\mathrm{mW}]$ medido (0,81V@8MHz) del SoC Digi            |       |

|       | neuron<br>V3a, realizando solo transferencias de datos ( $mu$ P y DMAs),           |       |

|       | con diferentes configuraciones de Ch<br>SymSim: a) kernel pequeños (1×1            |       |

|       | hasta $3 \times 3$ ; b) kernel grandes (hasta $9 \times 9$ )                       | . 294 |

| J.8.  | Consumo de potencia en $[\mathrm{mW}]$ calculado (1,07V@25MHz) del acele-          |       |

|       | rador ChSymSim en DigineuronV3a, ejecutando diferentes configura-                  |       |

|       | ciones: a) kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta           |       |

|       | $9 \times 9$ )                                                                     | . 295 |

| J.9.  | Consumo de potencia en $[\mathrm{mW}]$ calculado (0,81V@8MHz) del acele-           |       |

|       | rador ChSymSim en DigineuronV3a, ejecutando diferentes configura-                  |       |

|       | ciones: a) kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta           |       |

|       | $9 \times 9$ )                                                                     | . 296 |

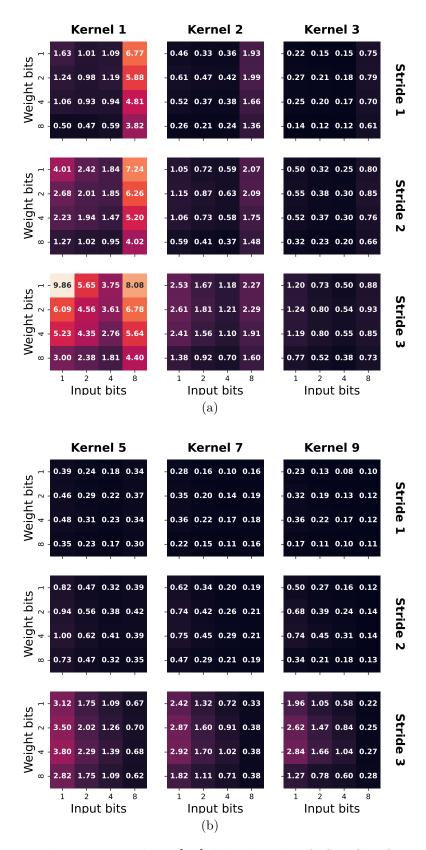

| J.10. | . Consumo de potencia en $[\mathrm{mW}]$ medido (2,1V@100MHz) del SoC Di-          |       |

|       | gineuronV3a, ejecutando diferentes configuraciones de ChSymSim: a)                 |       |

|       | kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9).              | . 297 |

| J.11. | . Consumo de potencia en $[\mathrm{mW}]$ calculado (2,1V@100MHz) del acele-        |       |

|       | rador ChSymSim en DigineuronV3a, ejecutando diferentes configura-                  |       |

|       | ciones: a) kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta           |       |

|       | $9 \times 9$ )                                                                     | . 298 |

| J.12. | . Consumo de potencia en $[\mathrm{mW}]$ medido (2,1V@100MHz) del SoC Di-          |       |

|       | gineuron<br>V3a, realizando solo transferencias de datos ( $mu$ P y DMAs),         |       |

|       | con diferentes configuraciones de Ch<br>SymSim: a) kernel pequeños (1×1            |       |

|       | hasta $3 \times 3$ ; b) kernel grandes (hasta $9 \times 9$ )                       | . 299 |

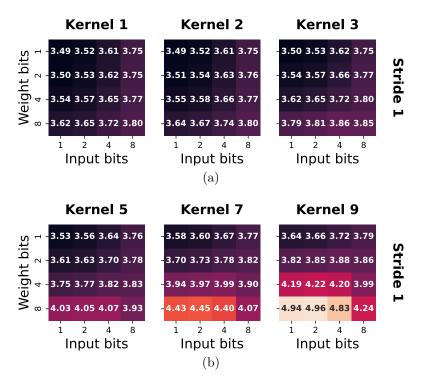

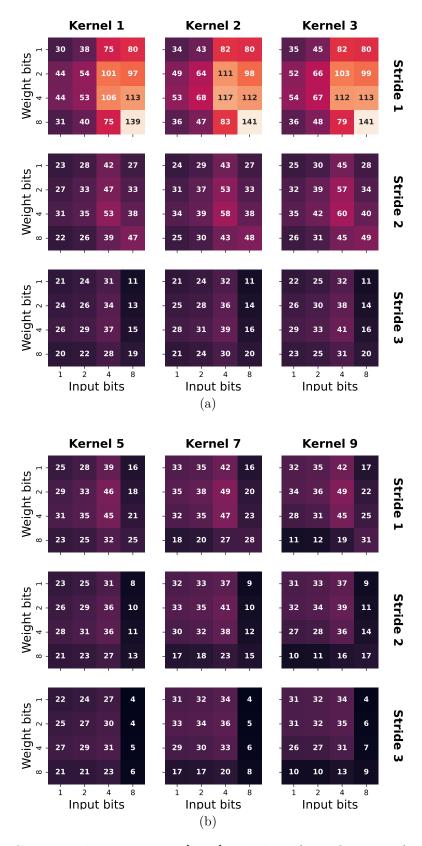

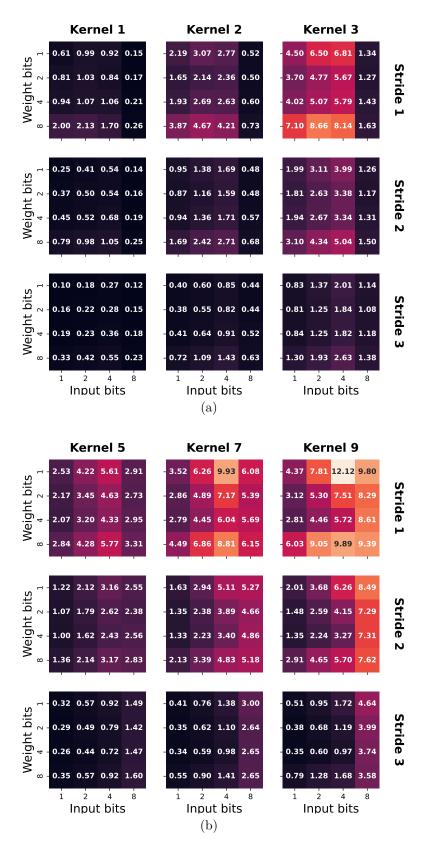

| K.1. | Energía media en [nJ] del acelerador ChSymSim (2,1V@100MHz),                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

|      | calculada por ciclo de procesamiento y ejecutando diferentes configu-                                                                   |

|      | raciones: a) kernel pequeños (1 $\times$ 1 hasta 3 $\times$ 3); b) kernel grandes                                                       |

|      | (hasta $9 \times 9$ )                                                                                                                   |

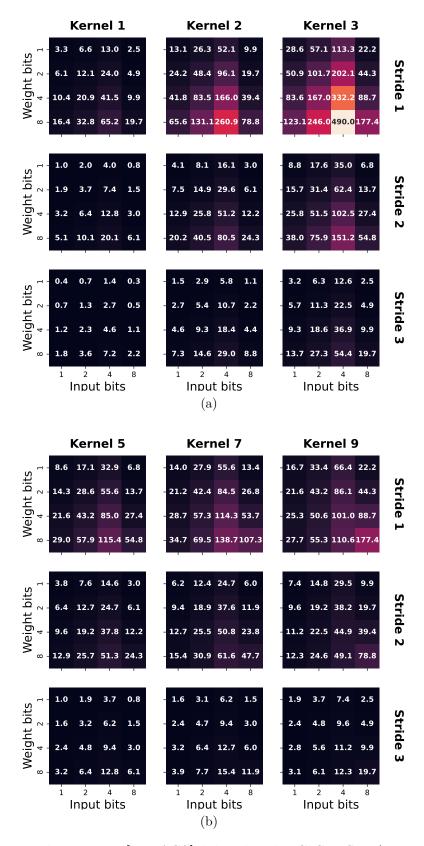

| K.2. | Energía media en $[\mathrm{nJ}]$ del acelerador Ch<br>SymSim (1,2V@25MHz), cal-                                                         |

|      | culada por ciclo de procesamiento y ejecutando diferentes configura-                                                                    |

|      | ciones: a) kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta                                                                |

|      | $9 \times 9$ )                                                                                                                          |

| K.3. | Energía media en [nJ] del acelerador ChSymSim (1,07V@25MHz),                                                                            |

|      | calculada por ciclo de procesamiento y ejecutando diferentes configu-                                                                   |

|      | raciones: a) kernel pequeños (1 $\times$ 1 hasta 3 $\times$ 3); b) kernel grandes                                                       |

|      | $(hasta 9 \times 9). \dots \dots$ |

| K.4. | Energía media en [nJ] del acelerador ChSymSim (0,81V@8MHz), cal-                                                                        |

|      | culada por ciclo de procesamiento y ejecutando diferentes configura-                                                                    |

|      | ciones: a) kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta                                                                |

|      | $9 \times 9$ )                                                                                                                          |

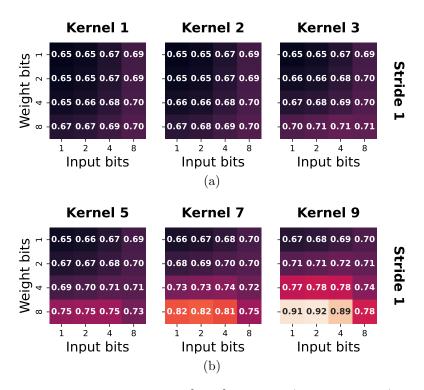

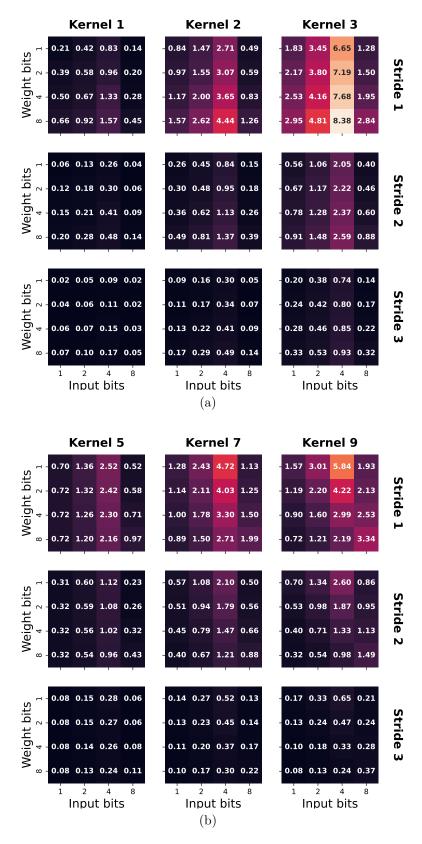

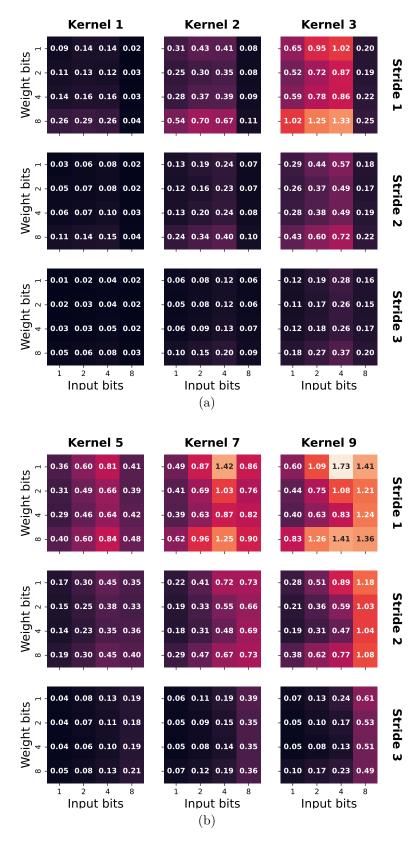

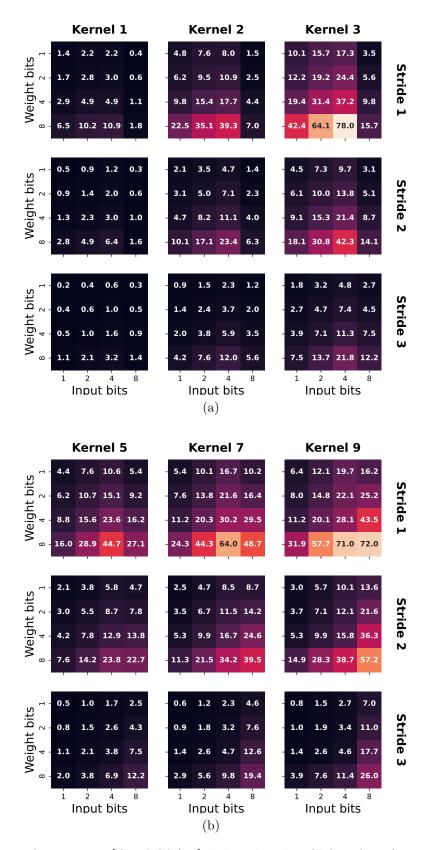

| K.5. | Energía por operación en $[\mathrm{pJ}]$ del acelerador ChSymSim (2,1V@100MHz),                                                         |

|      | con operaciones de 8 bits y ejecutando diferentes configuraciones: a)                                                                   |

|      | kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 305                                                                |

| K.6. | Energía por operación en [pJ] del acelerador Ch<br>SymSim (1,2V@25MHz),                                                                 |

|      | con operaciones de 8 bits y ejecutando diferentes configuraciones: a)                                                                   |

|      | kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 306                                                                |

| K.7. | Energía por operación en [pJ] del acelerador Ch<br>SymSim (1,07<br>V@25MHz),                                                            |

|      | con operaciones de 8 bits y ejecutando diferentes configuraciones: a)                                                                   |

|      | kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 307                                                                |

| K.8. | Energía por operación en $[\mathrm{pJ}]$ del acelerador ChSymSim (0,81V@8MHz),                                                          |

|      | con operaciones de 8 bits y ejecutando diferentes configuraciones: a)                                                                   |

|      | kernel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 308                                                                |

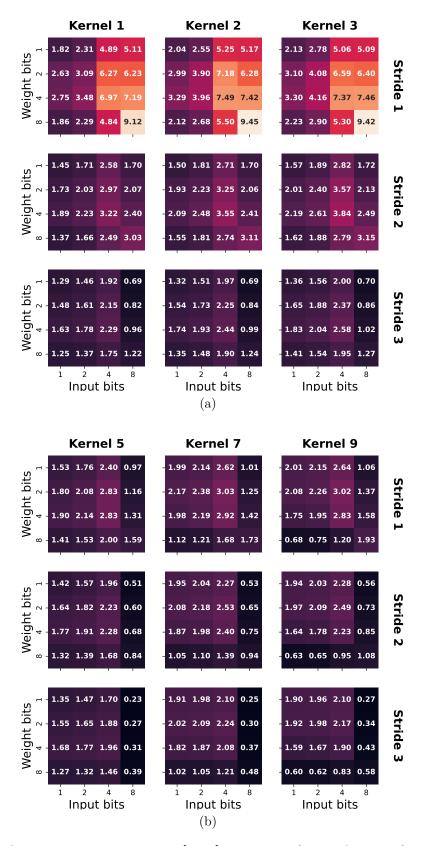

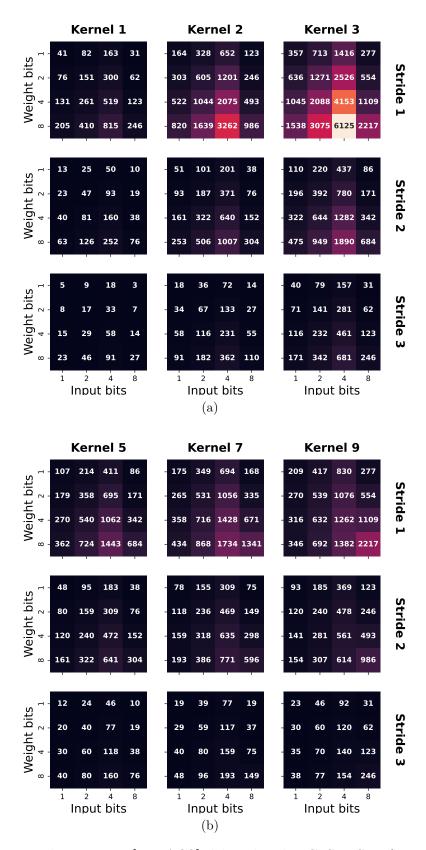

| K.9. | Rendimiento en [GOPS] del acelerador ChSymSim (operaciones de 8                                                                         |

|      | bits @100MHz), ejecutando diferentes configuraciones: a) kernel pe-                                                                     |

|      | queños $(1 \times 1 \text{ hasta } 3 \times 3)$ ; b) kernel grandes (hasta $9 \times 9$ ) 309                                           |

| K.10.Rendimiento en [GOPS] del acelerador ChSymSim (operaciones de                         |

|--------------------------------------------------------------------------------------------|

| $8~\mathrm{bits}~@25\mathrm{MHz}),$ ejecutando diferentes configuraciones: a) kernel pe-   |

| queños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 310                            |

| K.11.Rendimiento en [GOPS] del acelerador ChSymSim (operaciones de                         |

| 8 bits @8MHz), ejecutando diferentes configuraciones: a) kernel pe-                        |

| queños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 311                            |

| K.12.Rendimiento en [MMACS] del acelerador ChSymSim (operaciones de                        |

| 8 bits @100MHz), ejecutando diferentes configuraciones: a) kernel pe-                      |

| queños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 312                            |

| K.13.Rendimiento en [MMACS] del acelerador ChSymSim (operaciones de                        |

| 8 bits @25MHz), ejecutando diferentes configuraciones: a) kernel pe-                       |

| queños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 313                            |

| K.14.Rendimiento en [MMACS] del acelerador ChSymSim (operaciones de                        |

| 8 bits @8MHz), ejecutando diferentes configuraciones: a) kernel pe-                        |

| queños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 314                            |

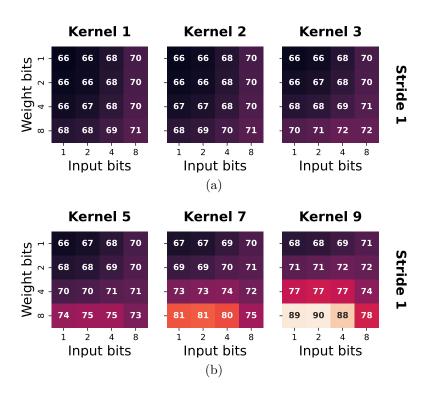

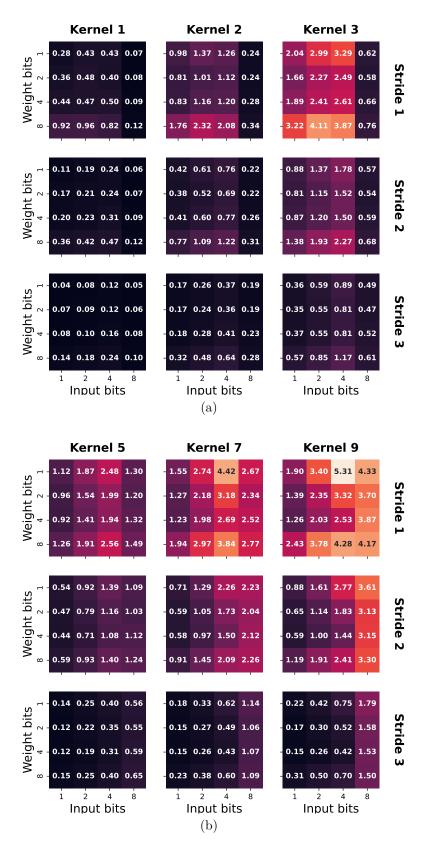

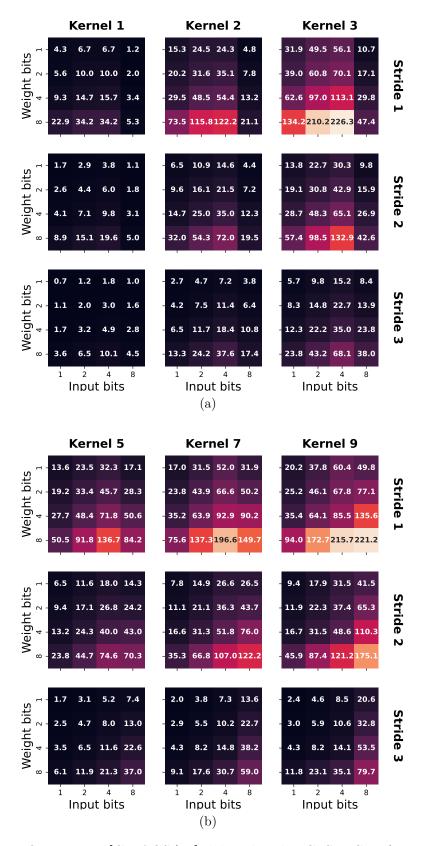

| $\rm K.15. Eficiencia en \ [TOPS/W]$ del acelerador Ch<br>SymSim (operaciones de $8$       |

| bits y $2.1V@100MHz$ ), ejecutando diferentes configuraciones: a) ker-                     |

| nel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 315                      |

| $\rm K.16. Eficiencia en \ [TOPS/W]$ del acelerador Ch<br>SymSim (operaciones de $8$       |

| bits y 1,2V@25MHz), ejecutando diferentes configuraciones: a) kernel                       |

| pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 316                          |

| $\rm K.17. Eficiencia en \ [TOPS/W]$ del acelerador Ch<br>SymSim (operaciones de $8$       |

| bits y 1,07<br>V@25MHz), ejecutando diferentes configuraciones: a) ker-                    |

| nel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 317                      |

| $\rm K.18.Eficiencia \ en \ [TOPS/W]$ del acelerador Ch<br>SymSim (operaciones de $8$      |

| bits y 0,81V@8MHz), ejecutando diferentes configuraciones: a) kernel                       |

| pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 318                          |

| K.19.Eficiencia en [GMACS/W] del acelerador ChSymSim (operaciones de                       |

| 8 bits y 2,1V@100MHz), ejecutando diferentes configuraciones: a) ker-                      |

| nel pequeños (1 $\times$ 1 hasta 3 $\times$ 3); b) kernel grandes (hasta 9 $\times$ 9) 319 |

| K.20.Eficiencia en [GMACS/W] del acelerador ChSymSim (operaciones de                                             |

|------------------------------------------------------------------------------------------------------------------|

| 8 bits y 1,2<br>V@25MHz), ejecutando diferentes configuraciones: a) ker-                                         |

| nel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 320                                            |

| $\rm K.21.Eficiencia$ en $\rm [GMACS/W]$ del acelerador Ch<br>SymSim (operaciones de                             |

| $8\;\mathrm{bits}\;\mathrm{y}\;1,\!07\mathrm{V}@25\mathrm{MHz}),$ ejecutando diferentes configuraciones: a) ker- |

| nel pequeños (1 × 1 hasta 3 × 3); b) kernel grandes (hasta 9 × 9) 321                                            |

| $\rm K.22.Eficiencia$ en $\rm [GMACS/W]$ del acelerador Ch<br>SymSim (operaciones de                             |

| 8 bits y 0,81V@8MHz), ejecutando diferentes configuraciones: a) ker-                                             |

| nel pequeños (1 $\times$ 1 hasta 3 $\times$ 3); b) kernel grandes (hasta 9 $\times$ 9) 322                       |

# Índice de tablas

| 3.1. | Clasificación del dataset GTSRB por parte de los modelos RSSNN,                    |

|------|------------------------------------------------------------------------------------|

|      | obtenidos en [9]                                                                   |

| 3.2. | Resultados de entrenamiento para la clasificación de USTC SmokeRS                  |

|      | con los modelos ResNet luego de 500 épocas                                         |

| 4.1. | Compresión de canales posibles para el acelerador ChSymSim 124                     |

| 4.2. | Eficiencia de No-Solapamiento para una capa con entrada de tamaño                  |

|      | $3\times 224\times 224$ (RGB), kernel de $7\times 7,$ $stride~2$ y $padding~3~132$ |

| 4.3. | Eficiencia de No-Solapamiento para una capa con entrada de tamaño                  |

|      | $16 \times 56 \times 56$ , kernel de $3 \times 3$ , stride 2 y padding 1           |

| 4.4. | Factores de escala de compuertas lógicas (aproximación) para estima-               |

|      | ción de área                                                                       |

| 4.5. | Resultados de área (en $mm^2$ ) de los diseños post-síntesis para los              |

|      | aceleradores ChSymSim y convolucional y sus bloques principales 160                |

| 5.1. | Mapa de memoria resumido del arreglo de entradas al acelerador                     |

|      | ChSymSim                                                                           |

| 5.2. | Mapa de memoria resumido para los parámetros del acelerador ChSym-                 |

|      | Sim                                                                                |

| 5.3. | Mediciones de potencia en [mW] del SoC DigineuronV3a para dife-                    |

|      | rentes valores de frecuencia y tensión de alimentación, para cómputos              |

|      | de capas Ch<br>SymSim con entradas de " $q$ " bits y pesos " $p$ " (64 canales     |

|      | y 10 repeticiones)                                                                 |

| 5.4. | Mediciones de potencia en [mW] del SoC DigineuronV3a para di-                 |       |

|------|-------------------------------------------------------------------------------|-------|

|      | ferentes valores de frecuencia y tensión de alimentación, realizando          |       |

|      | solamente control y transferencia de datos (64 canales y 10 repeticio-        |       |

|      | nes)                                                                          | 202   |

| 5.5. | Estimación de potencia en [mW] del acelerador ChSymSim en Digi-               |       |

|      | neuronV3a, para diferentes valores de frecuencia y tensión de alimen-         |       |

|      | tación, realizando cómputos con entradas de "q" bits y pesos de "p"           |       |

|      | (64 canales y 10 repeticiones)                                                | 204   |

| 5.6. | Medidas de energía, desempeño y eficiencia (resumidas) del acelerador         |       |

|      | Ch<br>SymSim en el SoC Digineuron<br>V3a, considerando $stride\ 1.\ \dots\ .$ | 210   |

| 5.7. | Comparativa entre los SoCs fabricados: DigineuronV1, V2 y V3a,                |       |

|      | donde "OPs" están normalizadas a sumas de 8 bits                              | 210   |

| 5.8. | Comparación de consumo y desempeño (promedio) de aceleradores                 |       |

|      | para Redes Neuronales en SoCs                                                 | 212   |

| 5.9. | Comparación de consumo y desempeño (promedio) de aceleradores                 |       |

|      | simpliciales y simétricos                                                     | 213   |

| D.1. | Arquitectura de ResNet18                                                      | 250   |

| D.2. | Arquitectura de ResNet04                                                      | 250   |

| D.3. | Arquitectura de ResNet06                                                      | 251   |

| D.4. | Arquitectura de Res<br>Net<br>06 para entrada de tamaño 64 × 64               | 251   |

| D.5. | Arquitectura de ResNet08                                                      | 251   |

| D.6. | Requisitos de memoria en [MB] para la ejecución de algunas arqui-             |       |

|      | tecturas ResNet.                                                              | 252   |

| F.1. | Consumo de potencia (simulación post-síntesis) de multiplexores con           |       |

|      | 25 entradas de $8$ bits, con $10$ iteraciones de entradas aleatorias          | 262   |

| H.1. | Mapa de memoria del bus AHB                                                   | 269   |

| H.2. | Mapa de acceso del bus AHB                                                    | 270   |

| H.3. | Mapa de memoria del $bus$ APB, con dirección base $0x20000000.$               | 270   |

| H.4  | Mapa de memoria del módulo SysCTRL, con dirección base 0x20030000             | 0.271 |

| H.5.  | Mapa interrupciones del microprocesador: selección según el modo de          |      |

|-------|------------------------------------------------------------------------------|------|

|       | operación                                                                    | 272  |

| I.1.  | Mapa de memoria para configuración del acelerador ChSymSim: re-              |      |

|       | sets de registros internos, controladores y bancos de memorias ( $buffers$ ) | .274 |

| I.2.  | Mapa de memoria (configuración general) del acelerador ChSymSim.             | 275  |

| I.3.  | Mapa de memoria para configuración del acelerador ChSymSim: ha-              |      |

|       | bilitación de señales " $transfer\_done$ " externas                          | 276  |

| I.4.  | Mapa de memoria para configuración del acelerador ChSymSim: pre-             |      |

|       | cisión de entradas y pesos simétricos                                        | 276  |

| I.5.  | Mapa de memoria para configuración del acelerador ChSymSim: ge-              |      |

|       | nerador de rampa.                                                            | 277  |

| I.6.  | Mapa de memoria para configuración del acelerador ChSymSim: másca-           |      |

|       | ras de habilitación de comparadores y bloques en PEs                         | 278  |

| I.7.  | Mapa de memoria para configuración del acelerador ChSymSim: con-             |      |

|       | figuración de escalado de salidas, padding y stride                          | 279  |

| I.8.  | Mapa de memoria para configuración del acelerador ChSymSim: flags.           | 280  |

| I.9.  | Mapa de memoria para configuración del acelerador ChSymSim: Mo-              |      |

|       | do Manual ( $Debug$ )                                                        | 281  |

| I.10. | Mapa de memoria para configuración del acelerador ChSymSim: Mo-              |      |

|       | do Manual ( $Debug$ )                                                        | 282  |

| I.11. | Mapa de memoria para configuración del acelerador ChSymSim: Señales          |      |

|       | de control ( $Debug$ )                                                       | 283  |

| I.12. | Mapa de memoria para configuración del acelerador ChSymSim: In-              |      |

|       | terrupciones para transferencia de datos con el $\mu P.$                     | 284  |

| I.13. | Mapa de memoria para configuración del acelerador ChSymSim: Ha-              |      |

|       | bilitaciones de señales $request$ y $done$ para transferencia de datos con   |      |

|       | los DMAs                                                                     | 285  |

| I.14. | Mapa de memoria de parámetros para la función ChSymSim: Máscara              |      |

|       | de Forma de $kernel~(SM)$ , Elementos Estructurantes $(SE)$ , pesos          |      |

|       | simétricos(W) y bias(B)                                                      | 286  |

| I.15. | Mapa de memoria completo del arreglo de entradas al acelerador        |

|-------|-----------------------------------------------------------------------|

|       | ChSymSim                                                              |

| I.16. | Mapa de direcciones (resumido) para las salidas del acelerador ChSym- |

|       | Sim                                                                   |

|       |                                                                       |

| K.1.  | Medidas de energía, desempeño y eficiencia (resumidas) del acelerador |

|       | ChSymSim en el SoC DigineuronV3a, considerando stride 1 300           |

## Acrónimos

| ML Aprendizaje de máquina - Machine Learning                                     | 31 |

|----------------------------------------------------------------------------------|----|

| NN Red neuronal - Neural network                                                 | 31 |

| FC Fully-connected                                                               | 32 |

| CNN Red neuronal convolucional - Convolutional neural network                    | 32 |

| GPU Unidad de procesamiento gráfico - Graphics Processing Unit                   | 32 |

| MAC Multiplicación y acumulación                                                 | 33 |

| <b>DNN</b> Red neuronal profunda - <i>Deep neural network</i>                    | 33 |

| IoT Internet de las cosas - Internet of Things                                   | 33 |

| ASIC Circuito integrado de uso específico - Application-Specific Integrated cuit |    |

| FPGA Field-Programmable Gate Array                                               | 33 |

| IC Circuito integrado - Integrated Circuit                                    | 34 |

|-------------------------------------------------------------------------------|----|

| CMOS Complementary Metal Oxide Semiconductor                                  | 34 |

| ChSymSim Simplicial Simétrica a Canales Separados - Channel-wise Symmetrical  |    |

| RTL Abstracción a nivel de registros - Register Transfer Level                | 37 |

| SRAM Memoria de acceso aleatorio estático - Static Random Access Memory       | 37 |

| SoC Sistema en Chip - System on Chip                                          | 37 |

| ReLU Unidad de rectificación lineal - Rectified Linear Unit                   | 38 |

| PE Elemento de procesamiento - Processing Element                             | 38 |

| <b>DMA</b> Acceso directo a memoria - <i>Direct Memory Access</i>             | 38 |

| VLSI Circuitos integrados de gran escala/complejidad - Very Large Scale Integ |    |

| GTSRB German Traffic Sign Recognition Benchmark                               | 41 |

| PReLU Parametric Rectified Linear Unit                                        | 45 |

| SGD Stochastic Gradient Descent                                      | 47 |

|----------------------------------------------------------------------|----|

| SLFN Single hidden Layer Feedforward neural Network                  | 47 |

| MSE Mean Squared Error                                               | 49 |

| CEL Cross-Entropy Loss                                               | 49 |

| <b>MLP</b> Perceptrón multi-capa - <i>Multi-Layer Perceptron</i>     | 52 |

| BatchNorm Normalización por grupos de muestras - Batch Normalization | 54 |

| Conv2D Convolución en dos dimensiones                                | 55 |

| MaxPool Filtrado por valor máximo                                    | 58 |

| AvgPool Filtrado por valor medio                                     | 58 |

| MinPool Filtrado por valor mínimo                                    | 61 |

| MNN Morphological Neural Network                                     | 62 |

| QAT Quantization Aware Training                                      | 68 |

| PWL Lineal a tramos - Piece-wise linear                              | 69 |

| ${f PWM}$ Modulación por ancho de pulsos - $Pulse$ -width modulation | 71  |

|----------------------------------------------------------------------|-----|

| SymSim Simplicial Simétrica - Symmetric Simplicial                   | 74  |

| ${m SE}$ Elemento Estructurante - $Structuring\ Element$             | 85  |

| Inf Valor Infinito                                                   | 93  |

| NaN Not a Number                                                     | 93  |

| AF Función de Activación - Activation Function                       | 98  |

| SM Shape Mask                                                        | 120 |

| MUX Multiplexor                                                      | 144 |

| QSPI Quad Serial Peripheral Interface                                | 169 |

| P&R Place and Route                                                  | 171 |

| GPIO General Purpose Input/Output                                    | 172 |

| AMBA Advanced Microcontroller Bus Architecture                       | 172 |

| AHB Advanced High-performance Bus                                    | 172 |

| <b>UART</b> Universal Asynchronous Receiver Transmitter | 173 |

|---------------------------------------------------------|-----|

| APB Advanced Peripheral Bus                             | 173 |

| ISA Instruction Set Architecture                        | 177 |

| OBI Open Bus Interface                                  | 177 |

| IP Propiedad intelectual - Intellectual Property        | 177 |

| $\mu P$ Microprocesador                                 | 177 |

| BIST Built-in Self-Test                                 | 178 |

| RF Radiofrecuencia                                      | 182 |

| I/O Entrada/Salida - Input/Output                       | 183 |

| SPI Serial Peripheral Interface                         | 186 |

| MQSPI Multi-Quad Serial Peripheral Interface            | 188 |

| FIFO First Input First Output                           | 188 |

| USB Universal Serial Bus                                | 193 |

| <b>API</b> Application Programming Interface                   |   | <br> | 194 |

|----------------------------------------------------------------|---|------|-----|

| SDK Software Development Kit                                   |   | <br> | 193 |

| PLL Phase-Locked Loop                                          |   | <br> | 195 |

| NoC Network-on-Chip                                            |   | <br> | 217 |

| LSB Bit menos significativo - Least Significant Bit            | t | <br> | 258 |

| <b>MSB</b> Bit más significativo - <i>Most Significant Bit</i> |   | <br> | 258 |

| SR set/reset                                                   |   | <br> | 274 |

## Capítulo 1

### Introducción

#### 1.1. Problemática y estado del arte

Durante las décadas pasadas, los algoritmos de Aprendizaje de Máquina (ML¹) y las Redes Neuronales (NN²) se volvieron populares a la hora de resolver tareas complejas, tales como reconocimiento y clasificación de imágenes, segmentación, regresión, entre otras, impulsados por el crecimiento exponencial de las capacidades de las computadoras. Estos algoritmos proveen un modelo matemático para representar el comportamiento de neuronas cuando son excitadas por impulsos eléctricos a través de sus dendritas. Cada neurona se modela como un sumador de entradas pesadas, y una función no lineal de salida. El número promedio de entradas a una neurona real es de miles o decenas de miles [10]. Esto resulta en un número excesivo para implementar electrónicamente incluso utilizando tecnologías avanzadas de circuitos integrados, lo que ha producido diferentes enfoques para la implementación de NNs.

Uno de estos enfoques ha sido el de plantear arquitecturas compuestas por arreglos regulares de celdas de procesamiento, con un número bajo de entradas y solo conexiones locales a las neuronas vecinas [11], lo que permite procesar numerosos datos en paralelo y de forma rápida al reducir la necesidad de una comunicación global. Por otra parte, debido a la reducida actividad que producen, son en general esquemas de un consumo de energía inherentemente bajo, en contraste con las arquitecturas

$<sup>^1\</sup>mathrm{Aprendizaje}$  de máquina -  $\mathit{Machine}\ \mathit{Learning}$

<sup>&</sup>lt;sup>2</sup>Red neuronal - Neural network

tradicionales en las cuales todos los datos son transmitidos a un procesador central que se ocupa de realizar los cálculos requeridos. Este enfoque se encuadra dentro de los métodos neuromórficos, es decir que está inspirado en la naturaleza biológica de las neuronas, y ha sido utilizado principalmente para el filtrado de imágenes y la realización de operaciones morfológicas [12]. Mediante extensiones para clasificación de imágenes y utilizando diversas capas de NNs, estos modelos han evolucionado hasta convertirse en las arquitecturas de Redes Neuronales Convolucionales (CNN³) como las conocemos hoy en día [13], con la identificación de dígitos escritos a mano como uno de los ejemplos más conocidos de aplicación.

En base a la disponibilidad de mayores recursos computacionales, en la forma de placas de GPU<sup>4</sup> o servidores dedicados, se plantearon estructuras más ambiciosas y con varias capas sucesivas de NNs [14], que generalmente se componen de numerosos filtros convolucionales seguidos de neuronas con conectividad completa (capas FC<sup>5</sup>). Este tipo de estructuras alcanza fácilmente decenas o centenas de millones de parámetros, que deben ser ajustados mediante algoritmos de optimización en base a una cierta cantidad de imágenes de entradas y sus salidas deseadas. Desde la primera red de estas características (AlexNet) [15], se han propuesto extensiones y modificaciones, las cuales han permitido mejorar notablemente las propiedades de clasificación [16–18]. Estas aplicaciones se han vuelto un elemento clave en el abanico de arquitecturas de procesamiento del tipo Biq Data, donde grandes cantidades de datos deben ser procesados en tiempo real, generalmente mediante centros de servidores que tienen un consumo energético elevado. En la actualidad, los sistemas de mayor rendimiento [19] alcanzan el Exaflop/s o EFLOPS (10<sup>18</sup> operaciones de punto flotante por segundo) pero con consumos superiores a los 20 MW, mientras que aquellos más enfocados a la eficiencia energética [20] (superando los 60 GFLOP-S/W) aún presentan grandes consumos de varias decenas o cientos de kW. Estos consumos de potencia se traducen en costos de alrededor de 35 millones de dólares en electricidad anual para los sistemas de mayor rendimiento y cientos de miles de dólares para los de mayor eficiencia, con costos de operación y mantenimiento que ya supera largamente el costo de capital. De hecho, el grueso del costo mayormente re-

$<sup>^3</sup>$ Red neuronal convolucional -  $Convolutional\ neural\ network$

<sup>&</sup>lt;sup>4</sup>Unidad de procesamiento gráfico - Graphics Processing Unit

<sup>&</sup>lt;sup>5</sup>Fully-connected

side en costos edilicios y de refrigeración. Son estas infraestructuras computacionales las que soportan muchas de las funciones "inteligentes" actualmente disponibles en los teléfonos celulares, cuyo ejemplo más clásico es la interpretación y traducción de voz. De manera que hay un interés creciente en el desarrollo de circuitos integrados más eficientes desde el punto de vista energético que sean capaces de llevar a cabo, al menos parcialmente, estas funciones.

Es debido a estos costos de procesamiento con grandes centros de datos, junto a la necesidad de minimizar las latencias presentes en la comunicación con estos, que surge el paradigma de aplicaciones edge y Internet de las Cosas (IoT<sup>6</sup>), entre los que se encuentran ejemplos tales como agricultura inteligente para riego óptimo [21], detección de anomalías en la salud de pacientes [22], navegación autónoma y semi-autónoma [23], entre otras. En estos entornos, se requiere agregar "inteligencia" a sistemas embebidos de manera que cálculos complejos como los de Redes Neuronales Profundas (DNN<sup>7</sup>) puedan ser realizados en los mismos dispositivos, minimizando así la comunicación a un intercambio de datos entre sensores y unidades de procesamiento conectadas a una red local. De esta forma, si se utiliza hardware de propósito general, como por ejemplo microcontroladores, se reduce el consumo energético pero se presentan extensos tiempos de cómputo, mientras que en el otro extremo, con GPUs embebidas se aceleran notablemente los tiempos de cómputos pero a costa de un consumo energético excesivo (decenas de watts que podrían drenar la batería del dispositivo en unos pocos minutos).

Es por esto que encontrar un balance entre la capacidad de cómputo y el consumo energético se vuelve crucial en este tipo de aplicaciones, lo que suele requerir de aceleradores dedicados en circuitos integrados (ASIC<sup>8</sup>), dado que una FPGA<sup>9</sup> posee gran versatilidad (ideal para la realización de prototipos) pero con consumos de potencia elevados. Existen múltiples ejemplos de esto en la literatura. En [24] se implementa un arreglo 2D de multiplicadores y acumuladores (MAC<sup>10</sup>), con precisión variable de 4 bits, 8 bits y 16 bits. El circuito logrado se fabricó en una tecnología

<sup>&</sup>lt;sup>6</sup>Internet de las cosas - *Internet of Things*

<sup>&</sup>lt;sup>7</sup>Red neuronal profunda - Deep neural network

<sup>&</sup>lt;sup>8</sup>Circuito integrado de uso específico - Application-Specific Integrated Circuit

<sup>&</sup>lt;sup>9</sup>Field-Programmable Gate Array

<sup>&</sup>lt;sup>10</sup>Multiplicación y acumulación

FDSOI de 28nm en 1,87mm<sup>2</sup> y alcanza una eficiencia entre 0,26 y 10 TOPS/W. El sistema descrito en [25] puede implementar filtros de tamaño  $5 \times 5$  y  $7 \times 7$ . El chip resultante (Origami) fue fabricado en una tecnología CMOS<sup>11</sup> UMC 65nm y utiliza tanto pesos como entradas de 12 bits. En la configuración de alta velocidad (500MHz) alcanza un pico de 196 GOPS, mientras que en términos de eficiencia los autores reportan 437 GOPS/W con 1,2V@500MHz y 803 GOPS/W para 0,8V@189MHz. El chip Eyeriss v2 [26] está fabricado en TSMC 65nm LP y utiliza una precisión de 8 bits para entradas/pesos y 20 bits para sumas de productos parciales. Las convoluciones se realizan por medio de 192 elementos de procesamiento que pueden ser configurados para computar distintos modelos, como por ejemplo AlexNet, con la que se reporta una eficiencia de 253,2 GOPS/W. [27] utiliza una estructura MAC con precisión de punto fijo de 24 bits. Los autores manifiestan lograr una precisión de reconocimiento similar a la lograda con 64 bits en punto flotante con doble-precisión. El chip fue fabricado en un die de  $4 \times 4 \text{mm}^2$  en 65nm, con una eficiencia de 1,42 TOPS/W (1,2V@125MHz) ante 16 bits de entradas y pesos. [28] implementa un procesador general en 65nm capaz de lograr 8,1 TOPS/W CNN o RNN (Recursive Neural Networks). Los autores muestran que una precisión dinámica con un mecanismo adaptativo y una longitud de palabra de 4 bits logra resultados similares a utilizar 32 bits en punto flotante. [29] presenta un acelerador fabricado en UMC 65nm y optimizado para CNN de pesos binarios que alcanza 1,5 TOPS a 1,2V. El circuito integrado presenta un área de 1,9 mm $^2$  y un consumo de potencia de  $895\mu W$ . El motor convolucional soporta kernels de varios tamaños (entre  $1 \times 1$  y  $7 \times 7$ ).

#### 1.2. Objetivo

Teniendo en cuenta esta problemática establecida en la Sección 1.1, el objetivo principal de esta tesis es explorar y desarrollar unidades de cómputo en *hardwa-re*, para ser implementadas en circuitos integrados (IC<sup>12</sup>) eficientes (priorizando en términos de bajo consumo) y que sean capaces de resolver Redes Neuronales Profundas (DNN) en sistemas con recursos limitados. Las funciones simpliciales son buenas

$<sup>^{11}</sup>Complementary\ Metal\ Oxide\ Semiconductor$

<sup>&</sup>lt;sup>12</sup>Circuito integrado - Integrated Circuit

candidatas para resolver Redes Neuronales (NN) con un consumo reducido, ya que estas cuentan con estructuras de cómputo eficientes en hardware [30–37]. Sin embargo, tales implementaciones se han limitado hasta el presente a pequeños arreglos que procesaban filtros simples o determinadas operaciones morfológicas (sin capacidad de aprendizaje), agrupando entradas en vecindarios de a lo sumo 3 × 3 elementos. Dichas arquitecturas fueron pensadas para hacer un solo filtro o capa, en lugar de aplicaciones de mayor tamaño como podría ser el cómputo de NNs completas, por lo que resulta necesario modificar estas estructuras de cómputo, añadiendo funcionalidades requeridas para el cálculo de NNs, tales como tamaño de kernel configurable, stride y padding, pero evitando agregar complejidad en términos de hardware que anulen los beneficios en eficiencia que presentan estas estructuras.

Como punto de partida para esta mejora u optimización, se debe elegir alguna variante de las funciones simpliciales que pueda emplearse para el cómputo de DNNs. En principio, la función simplicial pura sería una buena opción dada su versatilidad a la hora de representar un gran abanico de funciones, siempre que sean lineales a tramos, pudiendo también representar a cualquier función lineal estándar en capas FC o convolucionales. Desafortunadamente, los parámetros o pesos requeridos para el cómputo de este tipo de operación escala exponencialmente con el número de parámetros. Las capas FC generalmente presentan un enorme número de entradas, mientras que las convencionales, que fueron ideadas para reducir la cantidad de entradas por operación, pueden utilizar filtros con kernel de dimensiones  $5 \times 5$  o  $7 \times 7$ , lo que incrementa notablemente la cantidad de memoria que se requiere para guardar los parámetros de una función simplicial pura.

Considerando que la cantidad de memoria en chip es limitada y que las operaciones para introducir o sacar datos de memorias externas son las que producen un mayor consumo energético, la idea de utilizar a la función simplicial en su versión simétrica resulta más atractiva, ya que esta requiere de una cantidad de parámetros similar a las funciones lineales (FC o convolución) que tradicionalmente se usan en Redes Neuronales. En función de lo expuesto, para cumplir con el objetivo de generar hardware eficiente para el cómputo de DNNs, se utilizarán funciones simpliciales simétricas, explorando sus capacidades y limitaciones en entornos de ML, y realizando las modificaciones u optimizaciones que se requieran para dicha tarea.

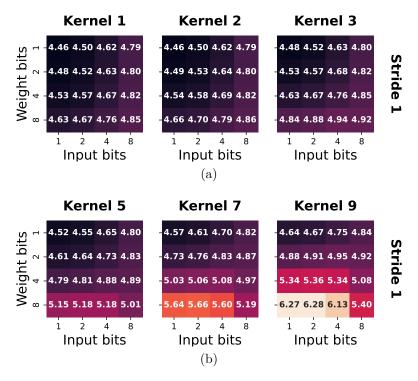

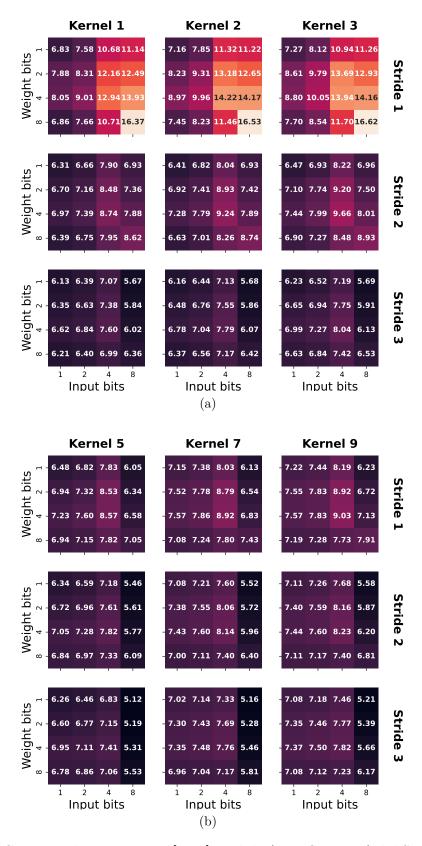

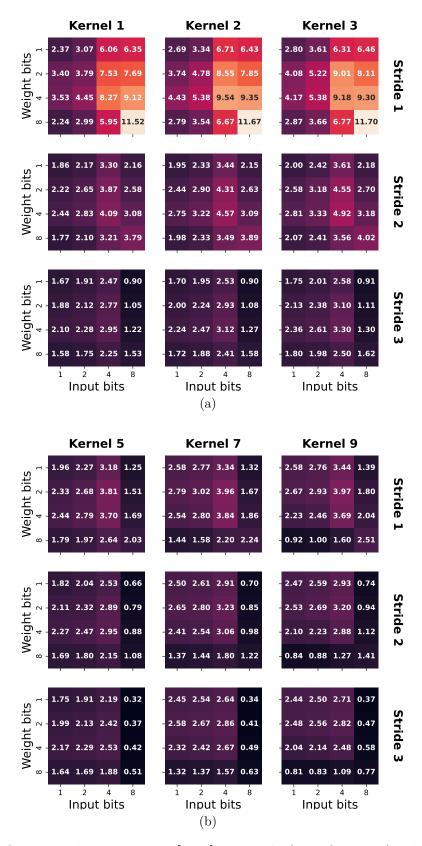

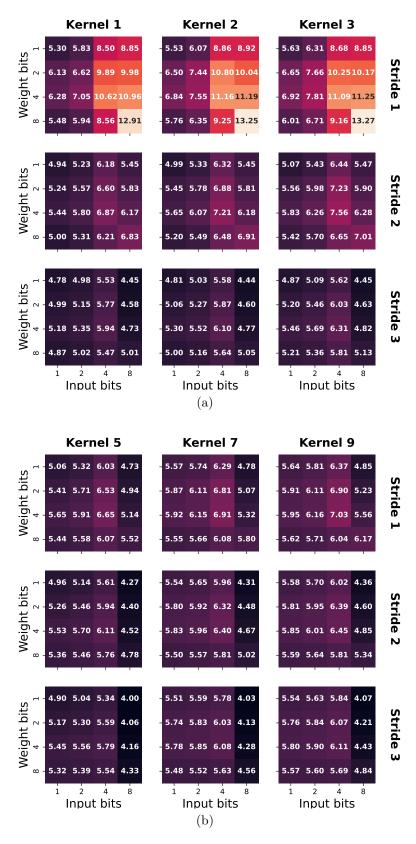

## 1.3. Contribución