UNIVERSIDAD NACIONAL DEL SUR

Tesis Magíster en Ingeniería

### DISEÑO DE CIRCUITOS INTEGRADOS DE BAJO CONSUMO PARA LA LOCALIZACIÓN DE FUENTES SONORAS

Franco Noel Martin Pirchio

BAHIA BLANCA ARGENTINA

### **Prefacio**

Esta Tesis se presenta como parte de los requisitos para optar al grado Académico de Magíster en Ingeniería, de la Universidad Nacional del Sur y no ha sido presentada previamente para la obtención de otro título en esta Universidad u otra. La misma contiene los resultados obtenidos en investigaciones llevadas a cabo en el grupo de investigaciones en sistemas electrónicos y electromecatrónicos (GISEE), dependiente del Departamento de Ingeniería Eléctrica y de Computadoras durante el período comprendido entre el 13 de marzo de 2006 y el 15 de Marzo de 2008, bajo la dirección del Dr. Pedro Marcelo Julián, Profesor Asociado de la Universidad Nacional del Sur e Investigador Independiente del CONICET.

| Fecha presentación: Diciembre 2011 |                          |

|------------------------------------|--------------------------|

|                                    | Franco N. Martin Pirchio |

DEPARTAMENTO DE INGENIERÍA ELÉCTRICA Y DE COMPUTADORAS

UNIVERSIDAD NACIONAL DEL SUR.

### **Agradecimientos**

Le agradezco a Pedro Julián por darme la oportunidad de desarrollarme en el campo de la microelectrónica y por mantenerme en el camino hacia la culminación de esta tesis. A Pablo Mandolesi, por compartir su tiempo y esfuerzo ante las dudas que surgieron durante el desarrollo de este trabajo. A los Jurados, Carlos F. Dualibe y Eduardo Paolini, por sus correcciones y comentarios.

A los amigos del Lab: Santiago, Martín, Gustavo, Seba, Hernán y Silvana; por hacer que las jornadas de trabajo hayan sido tan divertidas como productivas.

Especialmente le que quiero agradecer a Alfonso por haber compartido, codo a codo, tantas horas de esfuerzo y trabajo durante el desarrollo de los chips y las pruebas de campo.

Finalmente, agradezco el apoyo incondicional que tuve por parte de mi familia y Caty en el transcurso de estos años.

## Índice

| Prefacio                                         |            |

|--------------------------------------------------|------------|

| Agradecimientos                                  | iii        |

| Índice                                           | iv         |

| Lista de Figuras                                 | <b>v</b> i |

| Lista de Tablas                                  | ix         |

| Resumen                                          | X          |

| Abstract                                         | xi         |

| Capítulo 1                                       |            |

| Introducción y Resultados Existentes             | 1 -        |

| Introducción                                     | 1 -        |

| Organización de la Tesis                         | 2 -        |

| Resultados Preliminares                          | 2 -        |

| Algoritmo basado en la correlación (CA)          | 4 -        |

| Algoritmo de la derivada de la correlación (CCD) | 5 -        |

| Algoritmos neuromórficos (SA)                    |            |

| Algoritmo de gradiente espacial (SGA)            | 7 -        |

| Realizaciones en silicio                         | 7 -        |

| Descripción del CI CCD                           | 8 -        |

| Capítulo 2                                       |            |

| Estimador de Tiempo Basado en Correlación        |            |

| Introducción                                     |            |

| Descripción del Algoritmo                        |            |

| Arquitectura del Sistema                         |            |

| Unidad de retardo                                |            |

| Unidad de cálculo                                |            |

| Realización del Circuito Integrado               |            |

| Implementación en Tecnología CMOS de 0,5µm       |            |

| Implementación en Tecnología CMOS de 0,35 µm     |            |

| Resumen y comentarios                            | 37 -       |

| Capítulo 3                                       |            |

| Resultados experimentales                        |            |

| Introducción                                     |            |

| Ensayo del CI CCD en Cascada                     |            |

| Descripción de circuitos y placa de ensayo       |            |

| Descripción de las señales de prueba             | 43 -       |

| Mediciones del CI CCD                            | - 43 -     |

| Ensayo del CI adaptivo                                             | 46 - |

|--------------------------------------------------------------------|------|

| Mediciones sobre el CI en tecnología de 0,5μm                      | 46 - |

| Mediciones sobre el CI en tecnología de 0,35µm                     |      |

| Resumen y comentarios                                              |      |

| Capítulo 4                                                         |      |

| Sistemas de Localización de Fuentes Sonoras para Redes de Sensores | 56 - |

| Introducción                                                       |      |

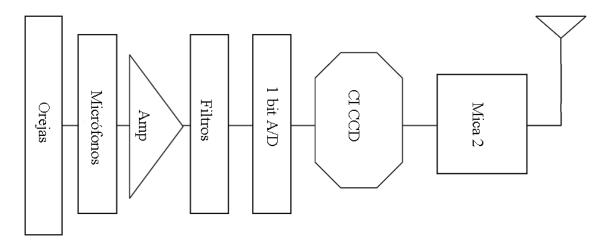

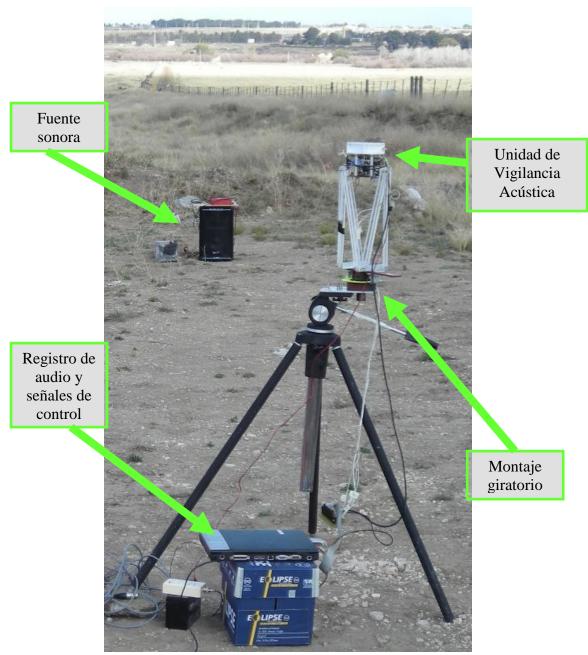

| Unidad de Vigilancia Acústica                                      | 56 - |

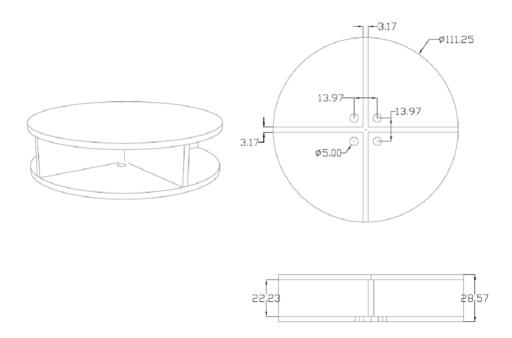

| Alojamiento para micrófonos                                        | 57 - |

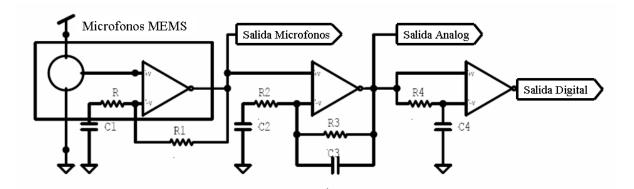

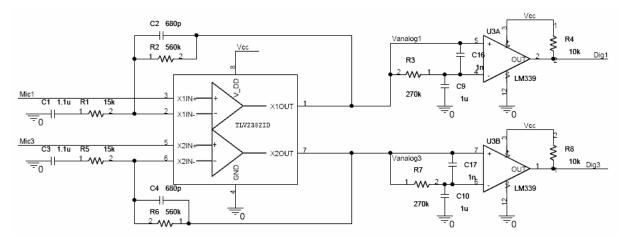

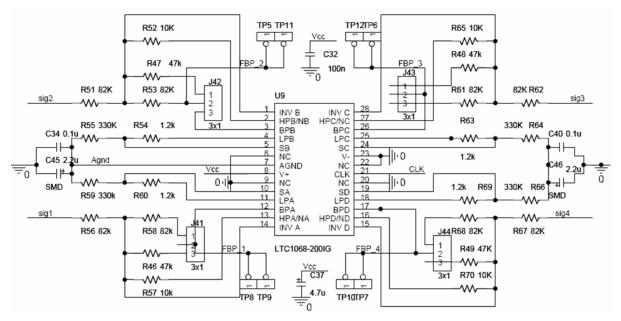

| Circuitos de acondicionamiento de señal                            | 58 - |

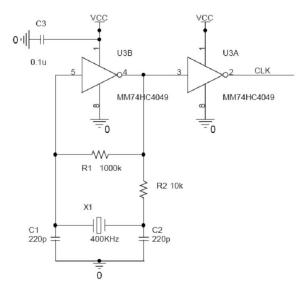

| Unidad de procesamiento digital                                    | 60 - |

| Unidad de RF                                                       | 61 - |

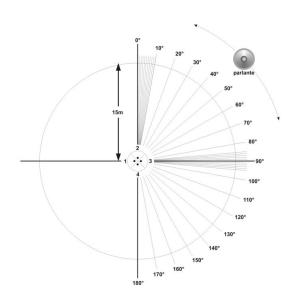

| Experimentos de campo.                                             | 62 - |

| Análisis Estadístico de Resultados Experimentales                  | 65 - |

| Descripción de la Nueva UVA                                        |      |

| Placa de micrófonos                                                | 66 - |

| Placa de filtros                                                   | 66 - |

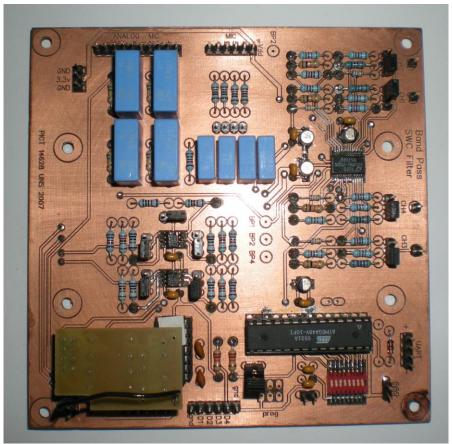

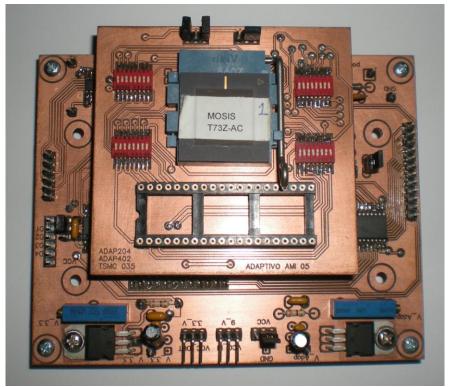

| Placa del CI                                                       | 69 - |

| Mediciones experimentales con UVA                                  | 72 - |

| Experiencias de laboratorio                                        | 72 - |

| Experiencias en campo                                              | 75 - |

| Resumen del ensayo de la UVA                                       | 84 - |

| Resumen y comentarios del capítulo                                 | 85 - |

| Capítulo 5                                                         |      |

| Conclusiones                                                       | 86 - |

| Apéndice I                                                         |      |

| Análisis Estadístico de Resultados Experimentales                  | 88 - |

| Planteo del problema                                               | 89 - |

| Conclusiones del análisis estadístico.                             | 97 - |

|                                                                    |      |

| Referencias                                                        | 98 - |

# Lista de Figuras

| Figura 1.1: Disposición del conjunto de micrófonos para la medición de ángulo de arrib |                                                                           |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Figura 1.2: Arquitectura general para correlación.                                     |                                                                           |

| Figura 1.3: Arquitectura del algoritmo de derivada de correlación.                     | 6 -                                                                       |

| Figura 1.4: Estructura del CI mostrando la cadena de retardos y los contadores         | 0                                                                         |

| ascendentes/descendentes.                                                              |                                                                           |

| Figura 1.5: Diagrama temporal con las señales de entrada, las señales de comando de lo |                                                                           |

| contadores y las nuevas señales de reloj.                                              |                                                                           |

| Figura 1.6: Conexionado en cascada para varios CI                                      |                                                                           |

| Figura 2.1: Conexión lógica entre bloques del algoritmo                                |                                                                           |

| Figura 2.2: Sistema de lazo cerrado para estimación de de retardo                      |                                                                           |

| Figura 2.3: Ejemplo de convergencia del sistema.                                       |                                                                           |

| Figura 2.4: Ejemplo de seguimiento de retardos variables.                              |                                                                           |

| Figura 2.5: Diagrama en bloque del sistema                                             |                                                                           |

| Figura 2.6: Esquema de la unidad de memoria                                            |                                                                           |

| Figura 2.7 Esquema de la unidad de cálculo                                             |                                                                           |

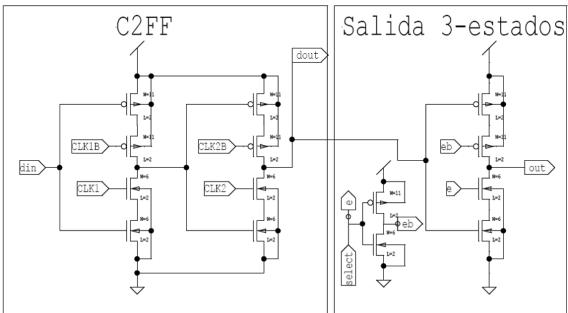

| Figura 2.8: Registro C <sup>2</sup> MOS y compuerta inversora 3 estados                | 22 -                                                                      |

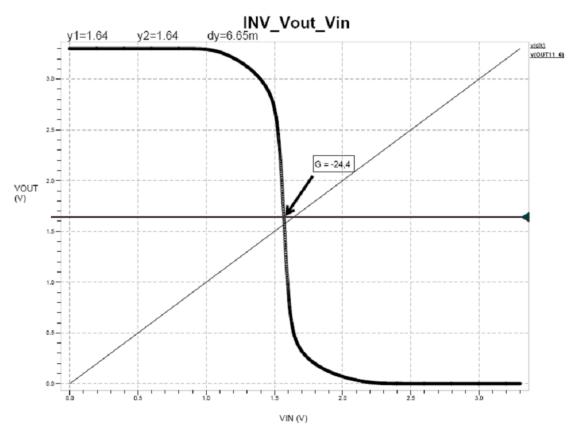

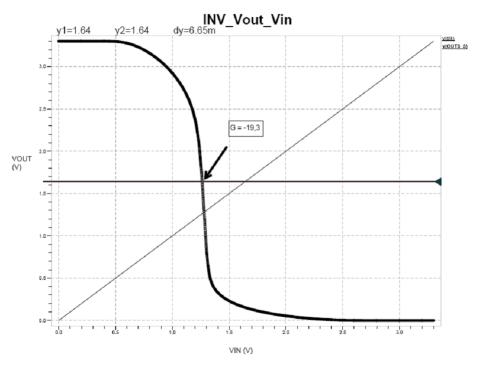

| Figura 2.9: Curva de transferencia de una compuerta inversora en tecnología CMOS de    |                                                                           |

| 0,5μm                                                                                  | 23 -                                                                      |

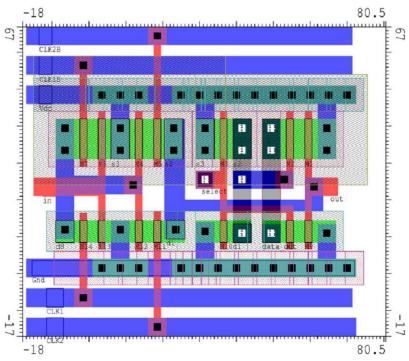

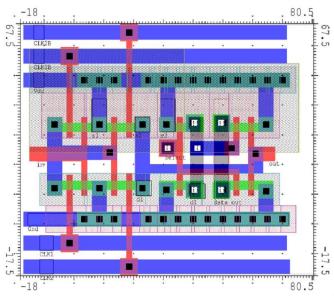

| Figura 2.10: Layout de un registro y su compuerta de salida en tecnología CMOS de 0,5  | iμm                                                                       |

| 24 -                                                                                   |                                                                           |

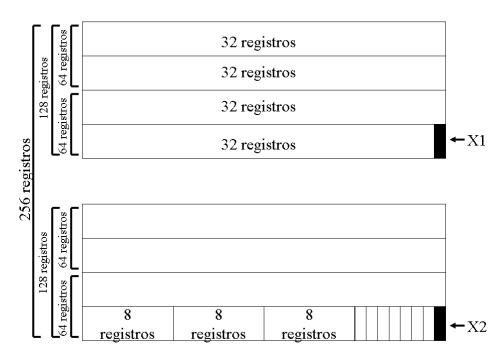

| Figura 2.11: Distribución de la memoria.                                               | 24 -                                                                      |

| Figura 2.12: Circuito esquemático del decodificador de 128 registros                   | ~ ~                                                                       |

|                                                                                        | 25 -                                                                      |

| Figura 2.13: Etapas en la decodificación de un registro.                               |                                                                           |

| Figura 2.13: Etapas en la decodificación de un registro                                | 26 -                                                                      |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -                                                              |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -                                                              |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -                                                      |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -                                                      |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>31 -                                      |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>32 -                                      |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>32 -<br>33 -                              |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>31 -<br>32 -<br>33 -<br>e                 |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>31 -<br>32 -<br>33 -<br>e                 |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>31 -<br>32 -<br>33 -<br>e<br>34 -<br>35 - |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>31 -<br>32 -<br>33 -<br>e<br>34 -         |

| Figura 2.14: Multiplexores de selección de datos                                       | 26 -<br>26 -<br>27 -<br>31 -<br>31 -<br>32 -<br>33 -<br>e<br>34 -<br>35 - |

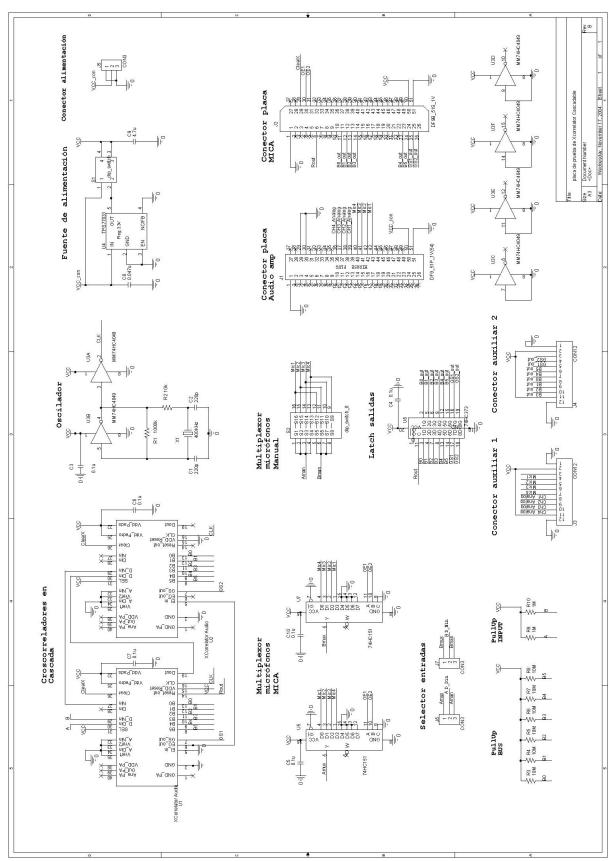

| Figura 3.1: Circuito esquemático de la placa de prueba.                             | 41 - |

|-------------------------------------------------------------------------------------|------|

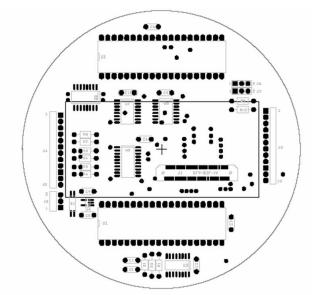

| Figura 3.2: Disposición de componentes de la placa de prueba                        | 42 - |

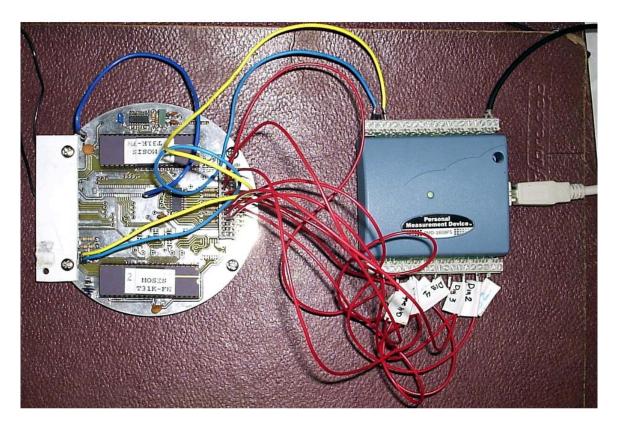

| Figura 3.3: Configuración para la medición de laboratorio de CI CCD                 | 42 - |

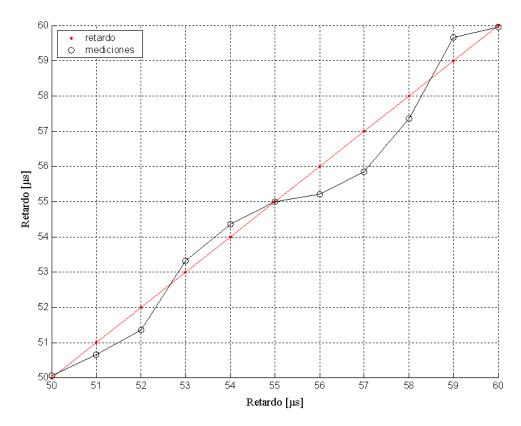

| Figura 3.4: Retardo medio en el rango 50 µs a 60µs.                                 | 44 - |

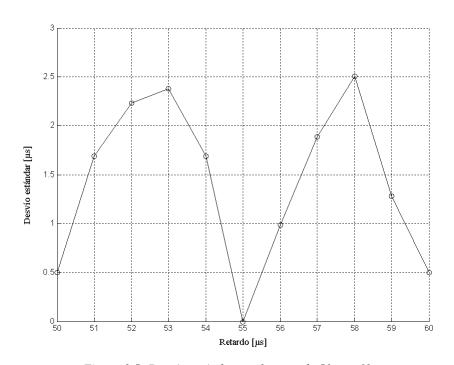

| Figura 3.5: Desvío estándar en el rango de 50µs a 60µs.                             | 44 - |

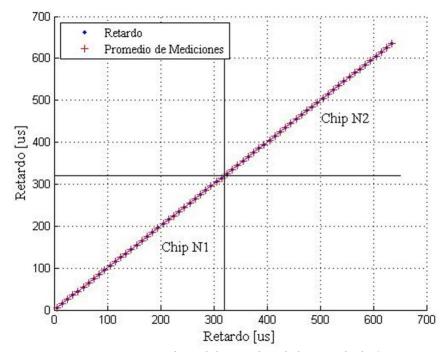

| Figura 3.6: Rango de medida completo de la cascada de CI's.                         | 45 - |

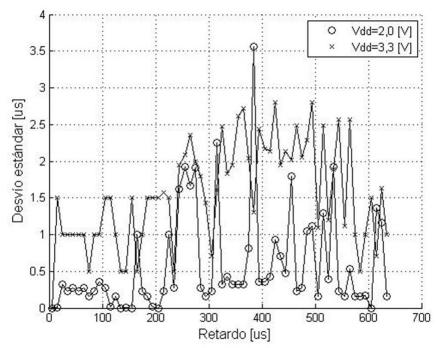

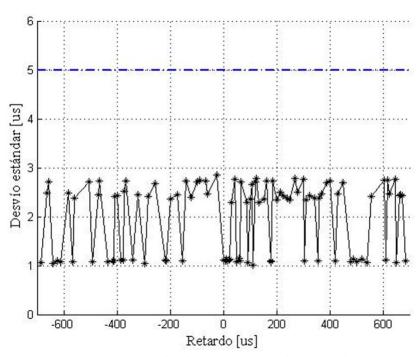

| Figura 3.7: Desvío estándar en el rango total de medición, para 3,3V y 2,0V         | 46 - |

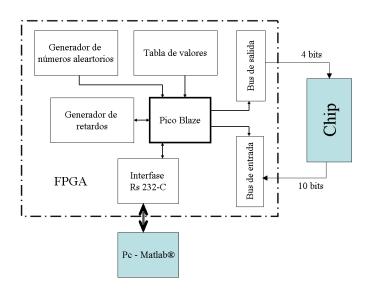

| Figura 3.8: Sistema para la verificación del CI                                     | 47 - |

| Figura 3.9: Fotografía del sistema de verificación                                  | 47 - |

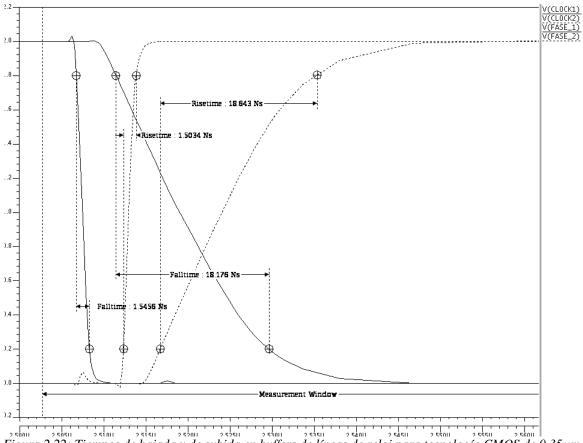

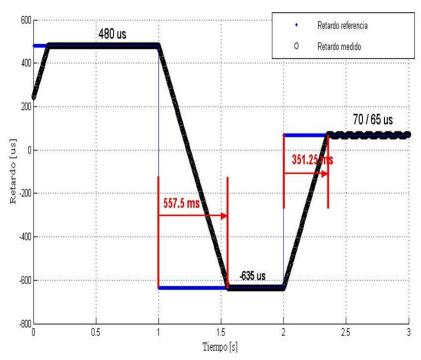

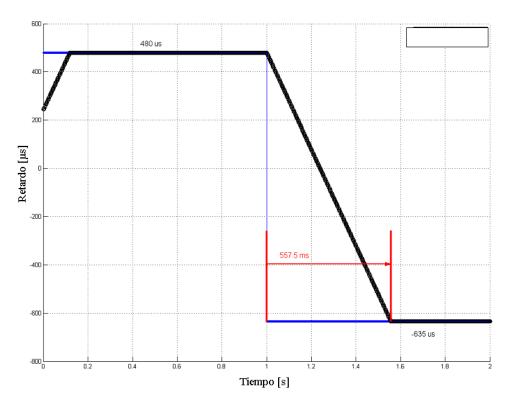

| Figura 3.10: Medición de tiempo de convergencia del CI                              | 48 - |

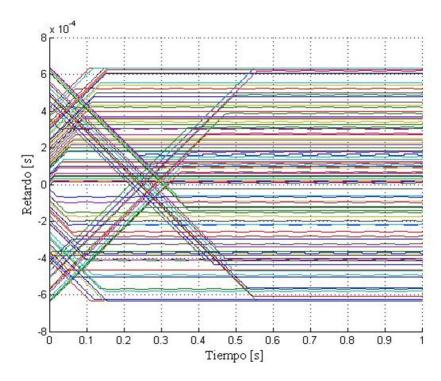

| Figura 3.11: Verificación del rango de medición del CI.                             | 49 - |

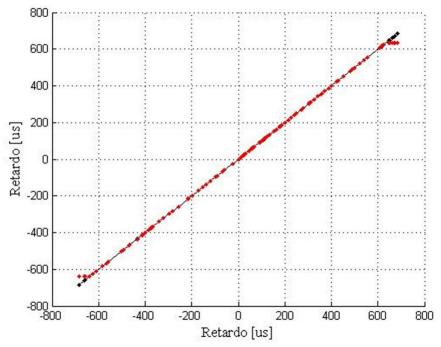

| Figura 3.12: Retardos promedio para el rango completo del CI                        |      |

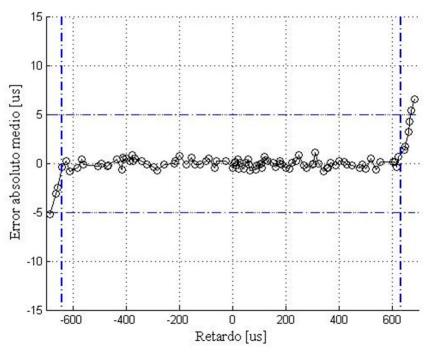

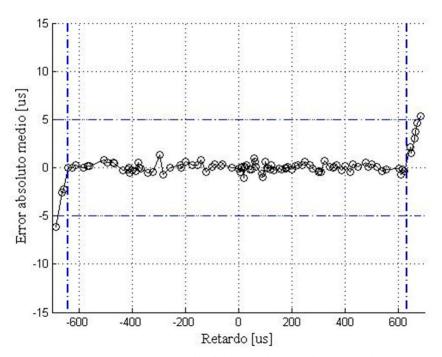

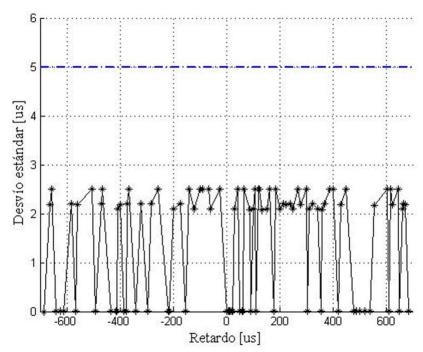

| Figura 3.13: Error absoluto medio del CI implementado en tecnología 0,5 µm          | 50 - |

| Figura 3.14: Desvío estándar del CI implementado en tecnología 0,5 µm               |      |

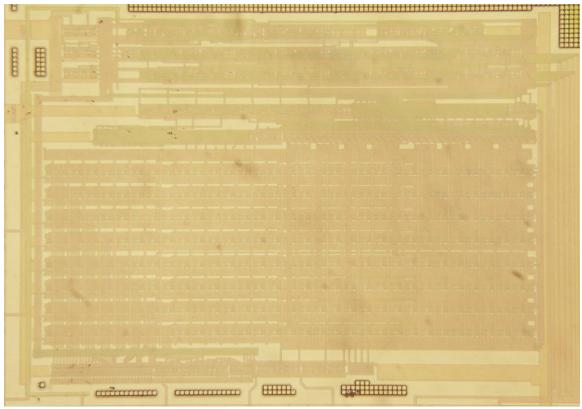

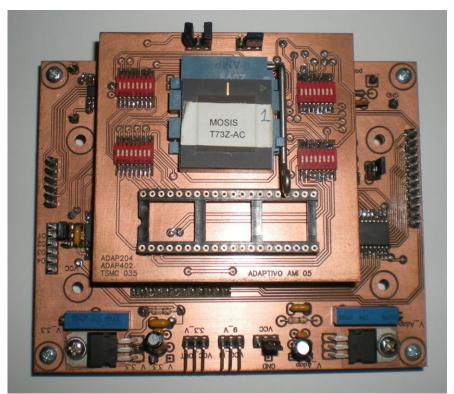

| Figura 3.15: Fotografía de la placa y el CI en el setup de prueba                   |      |

| Figura 3.16: Medición del tiempo de convergencia del CI                             |      |

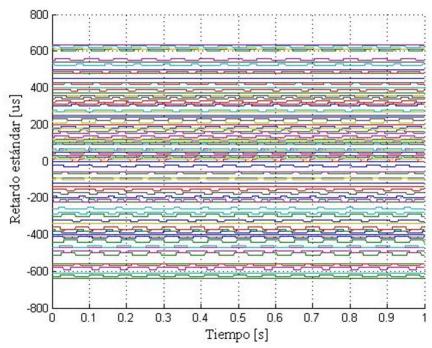

| Figura 3.17: Verificación del rango de medición.                                    |      |

| Figura 3.18: Error absoluto medio del CI implementado en tecnología 0,35µm          |      |

| Figura 3.19: Desvío estándar del CI implementado en tecnología 0,35µm               |      |

| Figura 4.1: Esquema de la unidad de vigilancia acústica.                            |      |

| Figura 4.2: Dimensiones del alojamiento acústico.                                   |      |

| Figura 4.3: Circuito esquemático de un canal de acondicionamiento de señal          |      |

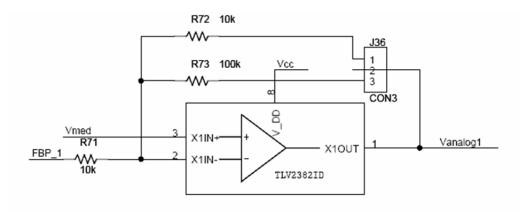

| Figura 4.4: Circuito esquemático de etapa de filtrado y conversión A/D              |      |

| Figura 4.5: Circuito esquemático del oscilador implementado con inversores          |      |

| Figura 4.6: Esquema del ensayo.                                                     |      |

| Figura 4.7: Configuración para mediciones en campo.                                 |      |

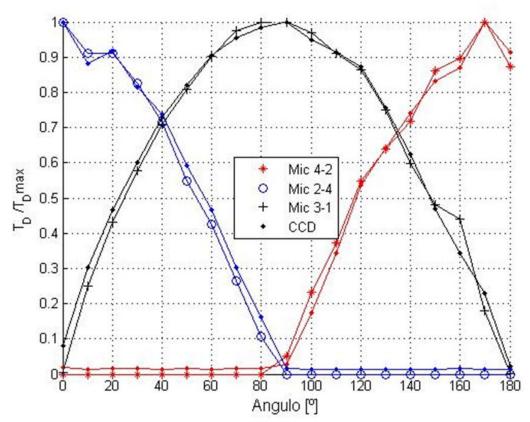

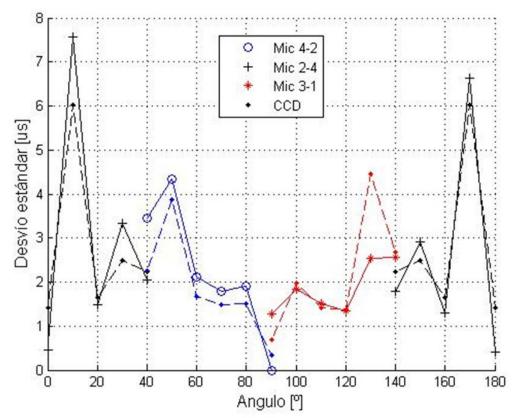

| Figura 4.8: Retardo normalizado versus ángulo de referencia                         |      |

| Figura 4.9: Desvío estándar del retardo según la combinación de micrófonos          |      |

| Figura 4.10: Circuito esquemático de los filtros pasa-banda                         |      |

| Figura 4.11: Circuito esquemático del amplificador                                  |      |

| Figura 4.12: Circuito esquemático del conversor A/D de 1bit.                        |      |

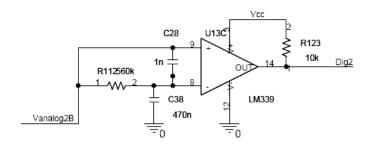

| Figura 4.13: Fotografía de la placa de filtros.                                     |      |

| Figura 4.14: Fotografía de la placa que aloja el CI                                 | 72 - |

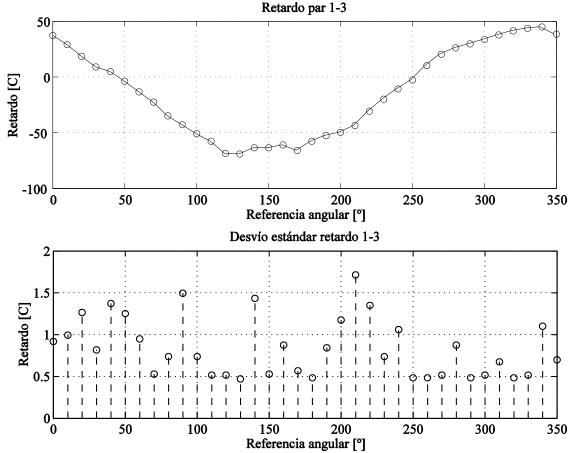

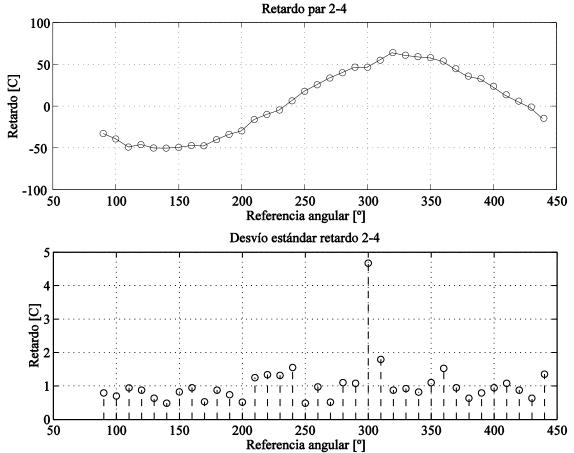

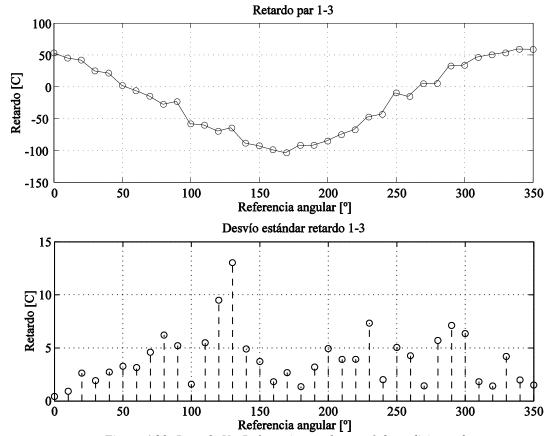

| Figura 4.15: Retardo Vs. variación angular, par 1-3                                 | 74 - |

| Figura 4.16: Retardo Vs. variación angular, par 2-4                                 |      |

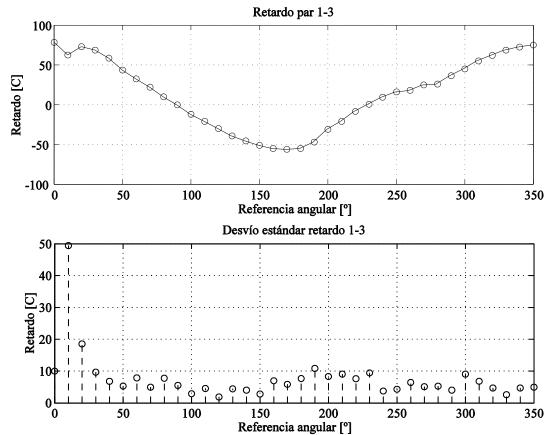

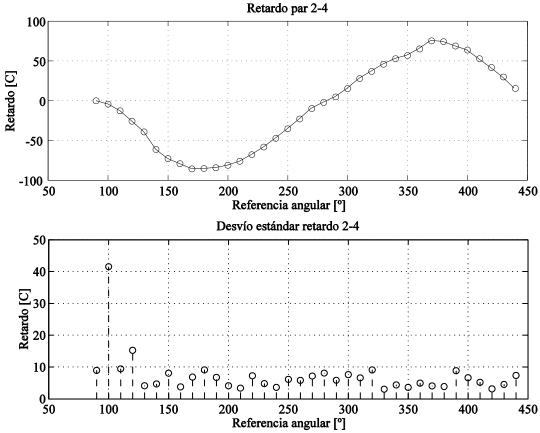

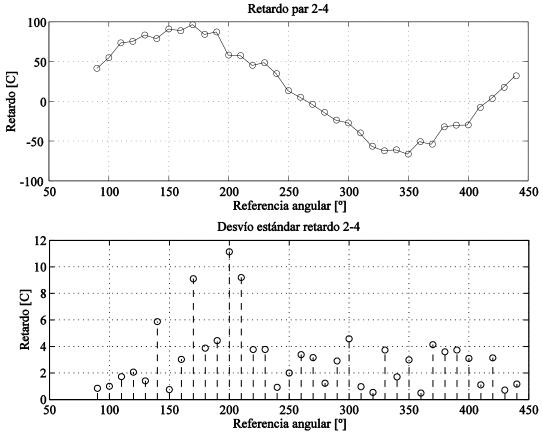

| Figura 4.17: Retardo medido en función del ángulo de referencia para el par 1-3     |      |

| Figura 4.18: Retardo medido en función del ángulo de referencia para el par 2-4     |      |

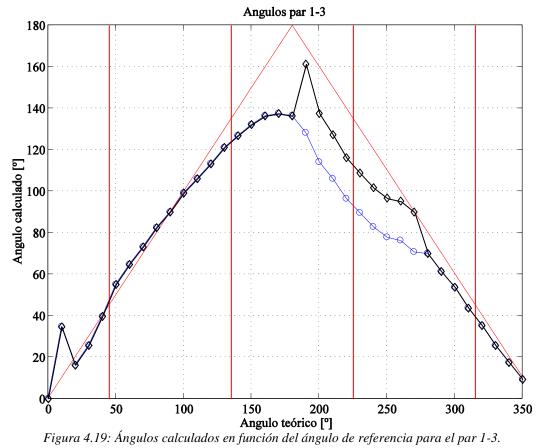

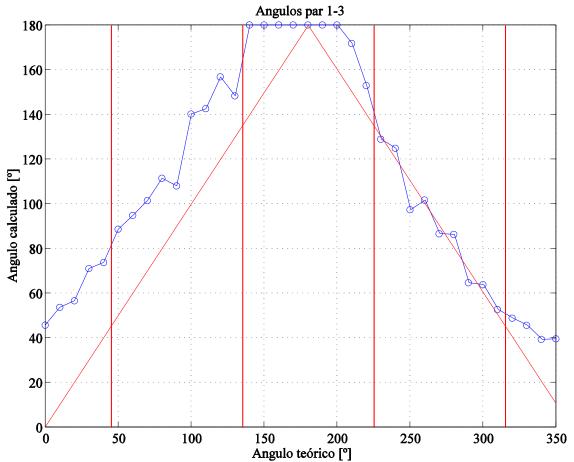

| Figura 4.19: Ángulos calculados en función del ángulo de referencia para el par 1-3 |      |

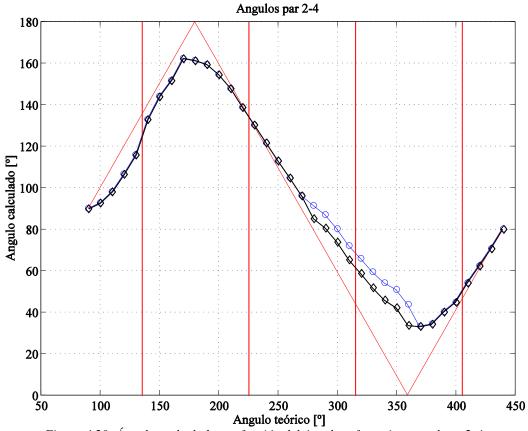

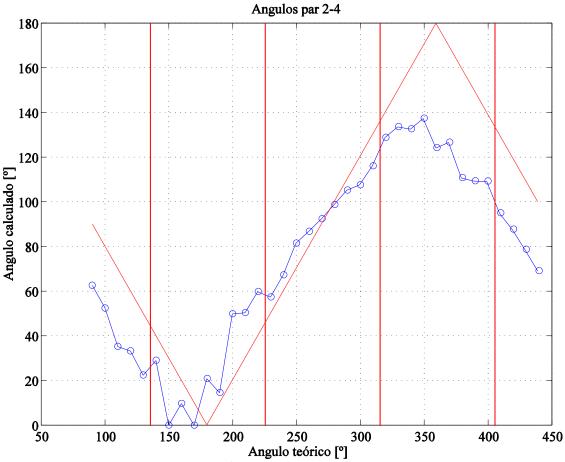

| Figura 4.20: Ángulos calculados en función del ángulo referencia para el par 2-4    |      |

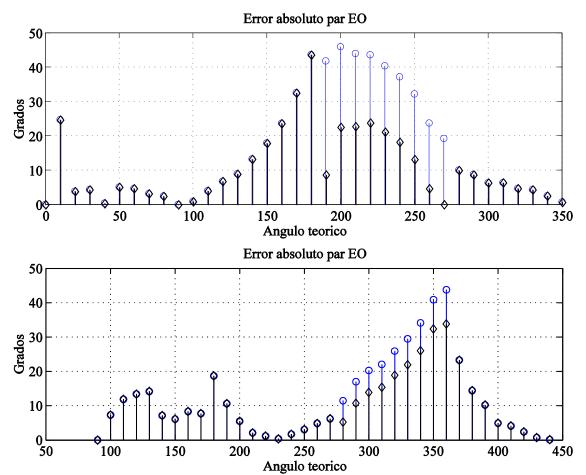

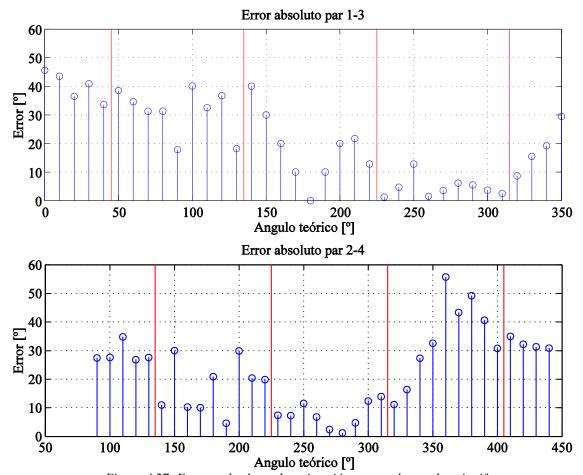

| Figura 4.21: Error absoluto en el cálculo de ángulos para ambos pares de micrófonos |      |

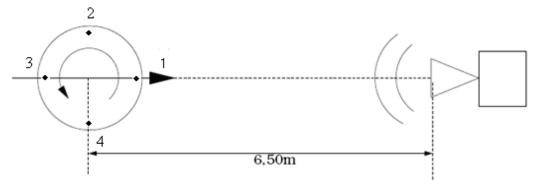

| Figura 4.22: Croquis de mediciones, segunda salida al campo.                        |      |

| Figura 4.23: Retardo Vs. Referencia angular par 1-3, mediciones de campo            |      |

| Figura 4.24: Retardo Vs. Referencia angular par 2-4, mediciones de campo            |      |

| Figura 4.25: Angulo de arribo estimado, par 1-3                                     |      |

| Figura 4.26: Angulo de arribo estimado, par 2-4.                                    |      |

| Figura 4.27: Errores absolutos de estimación para cada par de micrófonos            |      |

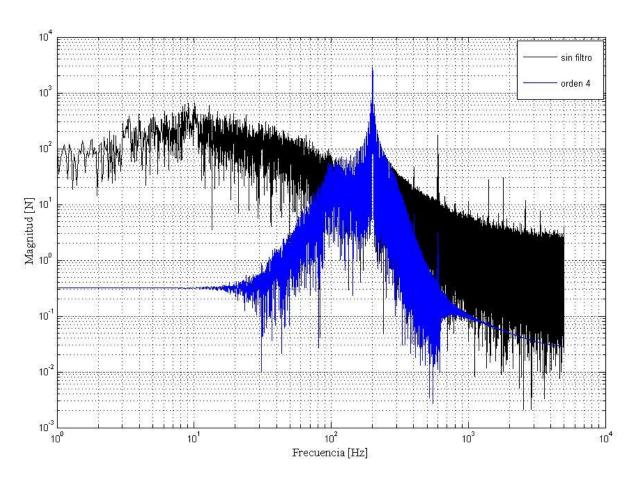

| Figura I.1: Espectros de las señales filtradas.                                     |      |

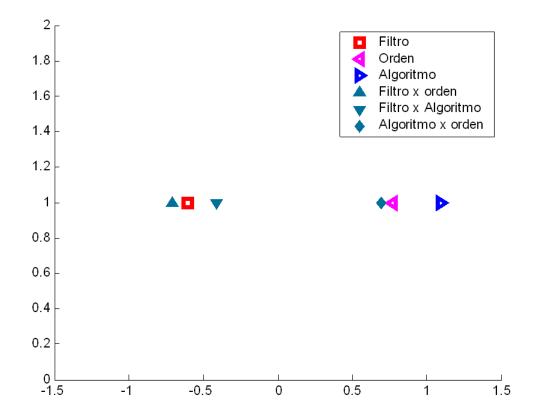

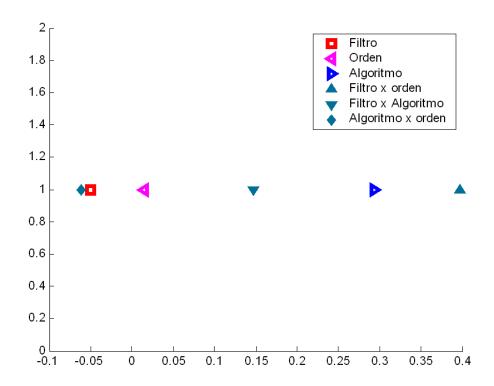

| Figura I.2: Efectos principales y secundarios.                                      |      |

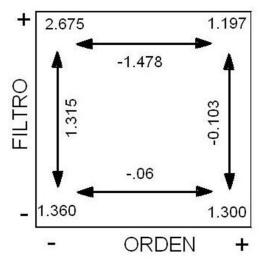

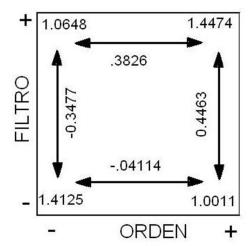

| Figura I.3: Interacción Filtro-Orden.                                               |      |

| Figura I 4: Efectos principales y secundarios                                       |      |

| Figura I.5: Interacción Filtro-Orden | 95 |

|--------------------------------------|----|

|--------------------------------------|----|

### Lista de Tablas

| Tabla 1.1: Precisión de los algoritmos (desvío estándar).                                 |       |

|-------------------------------------------------------------------------------------------|-------|

| Tabla 1.2: Comparación entre implementaciones de los algoritmos                           |       |

| Tabla 1.3: Tabla de verdad del funcionamiento de un CI CCD                                | 10 -  |

| Tabla 2.1: Tabla de verdad del algoritmo.                                                 |       |

| Tabla 2.2: Capacidades principales de una compuerta inversora en tecnología 0,5µm         | 28 -  |

| Tabla 2.3: Capacidades de líneas de reloj de un registro en tecnología 0,5μm              |       |

| Tabla 2.4: Carga absoluta y normalizada por línea de reloj, cantidad de etapas y relación | n de  |

| tamaños entre inversores                                                                  |       |

| Tabla 2.5: Tamaño de inversores en tecnología CMOS de 0,5 µm                              | 29 -  |

| Tabla 2.6: Factor de tamaño y tiempo de propagación de la cadena de inversores para el    | 1     |

| manejo de la línea de reloj, en función del número de etapas                              | 30 -  |

| Tabla 2.7: Área relativa y energía disipada por la cadena de inversores para el manejo d  | le la |

| línea de reloj, en función del número de etapas                                           |       |

| Tabla 2.8: Capacidades principales de una compuerta inversora en tecnología CMOS de       | e     |

| 0,35μm                                                                                    |       |

| Tabla 2.9: Capacidades de líneas de reloj de un registro en tecnología 0,35μm             | 35 -  |

| Tabla 2.10: Factor de tamaño y tiempo de propagación para cadena de inversoras en         |       |

| tecnología CMOS de 0,35µm.                                                                |       |

| Tabla 2.11: Áreas y energía disipada para cadena de inversoras en tecnología CMOS de      |       |

| 0,35μm                                                                                    |       |

| Tabla 3.1: Consumos por bloque del CI implementado en tecnología 0,5μm                    |       |

| Tabla 4.1: Consumo de potencia del CI medidor retardo CCD (a 3,3V)                        |       |

| Tabla 4.2: Consumos de la Unidad de Vigilancia Acústica (a 3,3V).                         |       |

| Tabla 4.3: Frecuencias y jitter del oscilador del filtro.                                 |       |

| Tabla 4.4: Combinación para selección de micrófonos.                                      | 71 -  |

| Tabla 4.5: Medición de retardo y su variación en la salida de amplificadores y de         |       |

| comparadores.                                                                             |       |

| Tabla I.1: Factores bajo estudio y sus combinaciones                                      |       |

| Tabla I.2: Datos codificados para el análisis.                                            |       |

| Tabla I.3: Retardos medios y varianzas de las muestras                                    |       |

| Tabla I.4: Resumen de efectos principales y secundarios                                   |       |

| Tabla I.5: Selección de datos para análisis filtro-orden                                  |       |

| Tabla I.6: Interacciones cruzadas entre filtros y orden                                   |       |

| Tabla I.7: Nuevo conjunto de datos a analizar                                             |       |

| Tabla I.8: Resumen de efectos principales y secundarios                                   |       |

| Tabla I.9: Interacciones cruzadas entre filtros y orden                                   | 95 -  |

| Tabla I.10: Desvíos estándar para analizar la influencia del filtrado en la estimación 95 - |

|---------------------------------------------------------------------------------------------|

|                                                                                             |

|                                                                                             |

|                                                                                             |

|                                                                                             |

|                                                                                             |

|                                                                                             |

|                                                                                             |

### Resumen

Esta tesis presenta un algoritmo de bajo consumo para detectar la ubicación la localización de una fuente sonora y su implementación en dos circuitos integrados (CI) en tecnologías CMOS estándar de 0,5µm y 0,35µm. El algoritmo utiliza un lazo de realimentación para estimar el retardo existente entre dos señales provenientes de un par de micrófonos. Gracias a este enfoque se disminuye la carga computacional y por lo tanto se reduce el consumo de potencia en los circuitos que lo implementen. Es capaz de medir adelantos o retrasos entre señales con una resolución de 8 bits (7 bits con signo) y una precisión de ½ bit. Para la realización circuital de este algoritmo se utilizaron técnicas de diseño de bajo consumo que se basan en el manejo adecuado de la actividad del reloj y en la aplicación de registros dinámicos como unidades de memoria. En el diseño de las máscaras se tuvieron en cuenta detalles referidos a la distribución de señales a fin de lograr una utilización eficiente del área de silicio. También en esta tesis se presentan resultados experimentales de ensayos desarrollados sobre tres CI. A través de estos resultados, obtenidos en laboratorio y en campo, se verificó el correcto funcionamiento de los mismos y se obtuvo el mejor desempeño (consumo y rango de medida) reportado hasta la fecha, en lo que se refiere a CI orientados a la localización de fuentes sonoras. Se diseñaron, construyeron y verificaron unidades que alojan los CI mencionados y son capaces de realizar la ubicación de fuentes sonoras. Sobre los resultados de experiencias de campo se aplicaron métodos de análisis estadístico para estudiar los efectos de las variaciones en el diseño de estas unidades.

### **Abstract**

This thesis presents a new algorithm for acoustic source localization that performs its action in a low power consumption mode. The thesis also presents two circuital implementations of it, showing two integrated circuits (IC) implemented in  $0.5\mu m$  and  $0.35\mu m$  CMOS standard process.

The algorithm uses a closed loop approach to estimate the existing delay between two signals incoming from a pair of microphones. Thanks to this focus, the computational complexity can be reduced and therefore the power consumption of the circuit can also be reduced. The features of the IC are that it can measure positive and negatives delays with a resolution of 8 bits (7 bits plus a bit sign) and a precision of ½ bit all over the measurement range. For the circuital realization of this algorithm low power consumption design techniques were used; basically an adequate management of the clock activity and the used of dynamic registers as a memory cells. A carefully mask design was made in order to achieve an efficient utilization of the silicon area. Also in this thesis experimental results from three IC test are shown, being all of them designed to perform time delay measurement. Through these results obtained in a laboratory and in the field, a functional verification was made showing a correct operation of the IC's. The best performance in power consumption and measurement range was reported for the adaptive closed loop approach. These results were compared to similar task IC's (acoustic source localization). A surveillance unit that works with the mentioned IC's was designed, built and tested, and it was able to localize acoustic sources. Field experiences were made and results from them where used into a statistical analysis way to study the performance changes effects based on the variation of design parameters. From the result of the analysis a new system was obtained that presents betters characteristics and functionalities that the previous one.

### Capítulo 1

### Introducción y Resultados Existentes

#### Introducción

Esta tesis está dedicada a la localización de fuentes sonoras en el rango de audio mediante la utilización de micrófonos y el procesamiento de las señales asociadas. En la literatura de localización de fuentes acústicas se han desarrollado e implementado diversas técnicas dentro de las que existen dos grupos bien diferenciados: las técnicas que realizan una detección coherente y las que realizan una detección no-coherente ([1], [2], [6]). En todas ellas se dispone de un conjunto de elementos transductores del sonido (micrófonos o hidrófonos) que generan señales eléctricas de acuerdo a las variaciones de amplitud y frecuencia que cada uno de ellos percibe en el medio. Cabe aclarar, que si bien el objeto de la medición es la presión acústica producida por la fuente deseada, la señal al propagarse e interactuar con el medio sufre variaciones, así como ruido e interferencias de otras fuentes acústicas no deseadas. Debido a esto, hay una cota de error mínima que depende en general de la relación señal a ruido, el escenario específico y el espectro característico de las señales. Por ello, es menester preprocesar las señales provenientes de los micrófonos mediante una etapa preamplificación y filtrado antes de procesar la señal para obtener la información de la ubicación de la o las fuentes sonoras. En particular, se plantea el problema de localización de una sola fuente acústica en un entorno abierto dentro de un sistema distribuido donde hay varios sensores comunicados en forma inalámbrica [2]. Estos sistemas conocidos como redes de sensores presentan numerosas ventajas en tareas de vigilancia y seguridad, dado que por un lado permiten lograr una buena estimación con sensores de baja calidad, y por otro lado, son más robustos ante fallas de sensores aislados. Uno de los proyectos en desarrollo en el grupo de investigación, que inspiró esta tesis, es la detección de vehículos en zonas rurales de la llanura pampeana. Estas redes presentan fuertes restricciones de consumo de potencia para los sensores y circuitos de procesamiento, por lo que el diseño debe estar orientado al bajo consumo desde la concepción del sistema. Existen consumos que están relacionados directamente con el área de cobertura que se pretende lograr con la red (potencia requerida por la comunicación inalámbrica) y otros consumos relacionados con la tarea a cumplir, la cantidad de información y procesamiento que se debe realizar [3].

En esta tesis se aplican técnicas novedosas para diseñar circuitos integrados (CI) de bajo consumo que permitan estimar el ángulo de arribo de una señal acústica a un par de micrófonos, a través de la medición del retardo relativo entre las señales (conocido en la liter atura como ITD, por su denominación en inglés "interaural time delay"). Se asume que la fuente de señal acústica se encuentra lo suficientemente alejada de los micrófonos, de tal

manera que se puede considerar el modelo de campo lejano; esto es, que el frente de onda que arriba a los micrófonos es plano. Esta suposición simplifica el modelo entre el ángulo de arribo y el tiempo de retardo, y hace a esta relación independiente de la distancia.

La tesis comienza con la medición y análisis de un circuito integrado basado en la correlación de las señales provenientes de los micrófonos, una vez que éstas han sido convertidas en señales digitales con solamente un bit de precisión. A partir de este circuito integrado se construyó una estación acústica con cuatro micrófonos, la cual se caracterizó y ensayó intensivamente en campo. Como segundo paso, se propuso una mejora del método de estimación del retardo que permite reducir el consumo de potencia, y mantener la precisión. La mejora consiste en la realización de un sistema adaptativo que define una función de error, y produce una acción de control que lleva un retardo genérico interno al chip a igualar el retardo entre las dos señales de entrada. Este circuito integrado se fabricó en dos tecnologías diferentes (AMI 0,5µm y TSMC 0,35µm), y su funcionamiento resultó adecuado. Una ventaja adicional del método propuesto, es que a diferencia de enfoques anteriores, puede realizar el seguimiento o tracking de una fuente en movimiento. Los circuitos integrados fabricados logran un consumo menor a los sistemas reportados en la literatura con exactitud equivalente. Por último, se diseñó una segunda estación acústica, con un filtro que aumenta la flexibilidad y reduce la varianza en la estimación, la cual se integró junto con los circuitos integrados y se validó en campo.

#### Organización de la Tesis

La tesis se organiza de la siguiente manera. En este capítulo se introduce el problema de la localización de fuentes acústicas relacionándolo con la medición de retardo. Se presentan los diferentes algoritmos para resolver este problema reportados en la literatura. Se describe también un CI diseñado para la medición de retardos que puede ser conectado en cascada para ampliar el rango de medición.

El Capítulo 2 presenta un nuevo algoritmo para la medición de retardos. Se describe su arquitectura y se presentan características de dos realizaciones del mismo en diferentes tecnologías de integración CMOS.

En el Capítulo 3 se presentan resultados experimentales obtenidos de CI implementados para la medición de retardos. En primer lugar se reportan resultados del CI en cascada que marcó el comienzo de mi trabajo dentro de la temática. Posteriormente se presentan los resultados obtenidos de los CI desarrollados dentro del marco de esta tesis: el primero de ellos desarrollado en tecnología CMOS de 0,5 µm y el segundo en tecnología CMOS de 0,35 µm.

El Capítulo 4 presenta el desarrollo, medición y análisis de una unidad destinada a la vigilancia de zonas rurales. Esta unidad es la que aloja los CI que realizan la medición de retardo.

Finalmente, en el Capítulo 5 se presentan las conclusiones de la tesis y se plantean futuras líneas de trabajo.

#### Resultados Preliminares

A continuación se presenta el marco general y se discuten diversas características de los algoritmos de localización de fuentes, sus implementaciones en sistemas y se presentan las características de un CI que implementa uno de estos algoritmos.

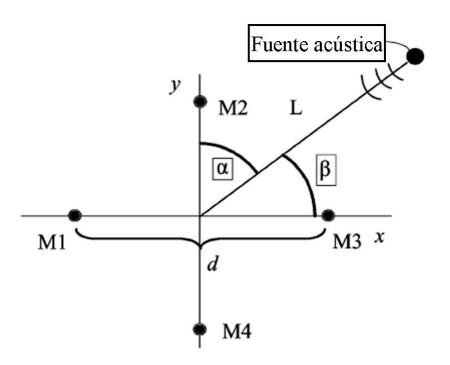

En líneas generales, el conjunto de micrófonos está formado por dos pares dispuestos en forma ortogonal sobre un círculo de diámetro d, como se muestra en la Fig. 1.1, sobre los

vértices de un cuadrado imaginario. También se puede ver en la figura que la dirección de la fuente acústica forma un ángulo  $\alpha$  con el eje de coordenadas y el par de micrófonos M2-M4, y un ángulo  $\beta$  con el par M1-M3.

El objetivo general es la estimación del ángulo que forma la fuente de sonido respecto del eje de coordenadas que tiene como origen el centro del círculo. Se supone que la separación entre micrófonos es mucho menor que la distancia a la cual se encuentra la fuente sonora; esto permite considerar la onda acústica como una onda plana por lo que la diferencia de tiempo entre los micrófonos solamente depende del ángulo de arribo.

Figura 1.1: Disposición del conjunto de micrófonos para la medición de ángulo de arribo.

Se considera el par de micrófonos M1-M3 y las señales que arriban a los mismos:

$$x_1(t) = s(t) + n_1(t) x_3(t) = s(t - T_D) + n_3(t)$$

(1.1)

En la literatura se han reportado numerosos algoritmos para realizar la estimación de  $T_D$  ([4],[5]). Los que presentan mejores características para ser implementados en circuitos integrados de señal mixta orientados a procesamiento en redes de sensores son los siguientes [7]:

- Algoritmos basados en Correlación (CA y CCD)

- Algoritmos de Gradiente espacial (SGA)

- Algoritmos Neuromórficos (SA)

Es destacable que estos algoritmos tienen un enfoque ideal para la implementación en redes de sensores, dado que realizan una detección coherente a nivel del nodo, evitando la necesidad de sincronizar temporalmente los nodos de la red. La sincronización se logra realizando varias transmisiones de difusión dentro de la red, lo genera un consumo extra de potencia en cada nodo [1].

#### Algoritmo basado en la correlación (CA)

La correlación entre dos señales puede representarse matemáticamente de la siguiente manera:

$$R_{x_1 x_3}(\tau) = \int_{-\infty}^{\infty} x_1(t) x_3(t+\tau) dt$$

(1.2)

Bajo la suposición general que el ruido de los micrófonos no está correlacionado, luego de reemplazar (1.1) en (1.2) se obtiene la expresión:

$$R_{x_1 x_3}(\tau) = \int_{-\infty}^{\infty} s(t)s(t - TD + \tau)dt \tag{1.3}$$

Dadas estas señales, la correlación entre ellas alcanzará el máximo para  $\tau = T_D$  por lo que el retardo se puede estimar evaluando la correlación y detectando el máximo. Tales operaciones imponen sobre el sistema la necesidad de contar con una ventana temporal de la señal durante la cual ésta será procesada.

Para realizar una implementación digital de este método las señales se deben muestrear cada Ts segundos. La resolución con la cual la señal es adquirida es de un bit. Como se demostrara en ([8], [9]) la autocorrelación de una señal y la autocorrelación de la misma señal pasaba por un bloque no lineal del tipo "infinity clip" (señal resultante es +1, 0, -1 si la señal de entrada es positiva, cero o negativa, respectivamente) retienen las características de periodicidad. Debido a esto, incrementar la resolución de la señal solo produce un incremento de la complejidad del hardware, sin un consiguiente aumento de la precisión del algoritmo. Esto fue evaluado numéricamente en [11].

La Ec. (1.4) presenta la versión discreta de la correlación entre las señales involucradas en este problema:

$$\tilde{R}_{x_1 x_3} (iTs) = \sum_{k=0}^{K} x_1 (kTs) x_3 ((k-i)Ts)$$

(1.4)

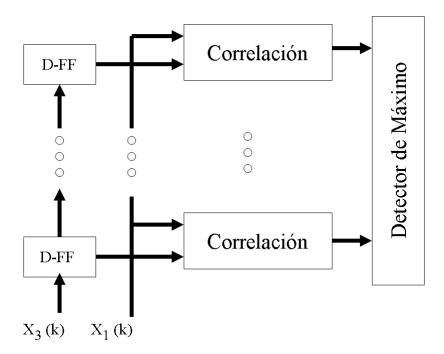

La reducción de la cantidad de bits de representación a sólo uno trae aparejada la ventaja de simplificar de forma sustancial la complejidad de la implementación en silicio. La Ec. (1.4) muestra que para realizar la correlación entre las señales se utiliza una ventana temporal de *K.Ts* segundos. La arquitectura basada en (1.4) consta de un número *K* de etapas formadas por correladores de un bit, como se ejemplifica en la Fig. 1.2.

Cada bloque de esta arquitectura trabaja a la frecuencia de muestreo y su salida proviene de un detector de máximo.

Figura 1.2: Arquitectura general para correlación.

Estas características producen una implementación voluminosa, debido a la necesidad de obtener el máximo de varias decenas de números digitales de al menos 8 bits, y motivó la realización de un nuevo algoritmo [10].

#### Algoritmo de la derivada de la correlación (CCD)

Si se puede garantizar que dentro de la ventana temporal de cálculo la correlación sólo tiene un máximo, éste puede detectarse a partir del cruce por cero de la derivada primera de la función correlación.

Con el cálculo de la diferencia discreta de dos elementos de cálculo de correlación adyacentes se obtiene:

$$\Delta y(i) = y(i) - y(i-1)$$

$$\Delta y(i) = \sum_{k=0}^{l} x_1(k) \left[ x_3(k-i) - x_3(k-(i-1)) \right]$$

(1.5)

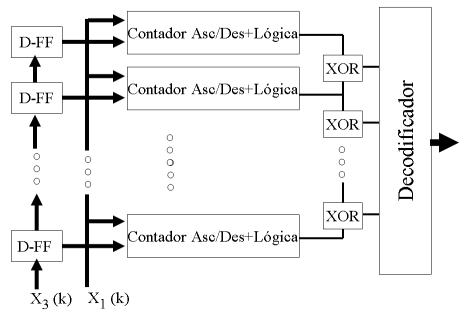

De (1.5) se desprenden varias implicaciones sobre la arquitectura que implementa el algoritmo. En primer lugar, los correladores pueden reemplazarse por contadores ascendentes-descendentes, y mediante una lógica adecuada, éstos pueden activarse solamente cuando hay cierta actividad en las señales de entrada. En segundo lugar, para realizar la detección del cero se puede detectar el cambio de signo de los contadores a través de la operación lógica OR exclusiva, ya que éstos cambian de negativo a positivo cuando hay un cruce por cero. Posteriormente a través de una decodificación de posición es posible obtener la ubicación del contador con el valor del cruce. Estas consideraciones llevan a una reducción de la actividad circuital y consecuentemente a la reducción del consumo de potencia. En la Fig. 1.3 se muestra un esquema general de la arquitectura.

Figura 1.3: Arquitectura del algoritmo de derivada de correlación.

En [11] se presenta un CI que implementa este algoritmo en un sistema de medición completo. Ese circuito exhibe un consumo de  $600\mu W$  y fue realizado en tecnología CMOS de  $0.35\mu m$ .

#### Algoritmos neuromórficos (SA)

El enfoque de esta línea de trabajo se basa en la imitación del procesamiento que realizan los organismos vivos, conocido como procesamiento neuromórfico. En este caso, existen en la literatura trabajos sobre modelos de cócleas en silicio para realizar implantes que permitan recuperar la audición ([12], [13], [14]). Basados en el modelado de las partes constitutivas del sistema auditivo humano y en el procesamiento a través de impulsos ("spikes") se han estudiado diferentes formas de realizar la detección y separación de fuentes sonoras ([15], [16]).

En [17] se plantea específicamente la implementación de esta clase de algoritmos para la estimación del ángulo de arribo de una señal acústica utilizando un par de micrófonos. Se propone un circuito de señal mixta, con una cóclea electrónica y un procesamiento inspirado en el algoritmo de "Stereausis" [18] para realizar la detección de una fuente acústica. Las señales en primer lugar se pasan a través de dos cadenas de filtros cocleares (una correspondiente al oído izquierdo, y otra al derecho). Luego, las señales analógicas son digitalizadas a un bit, realizando una comparación de nivel. Con estas señales digitalizadas se generan pulsos que tienen como duración el retardo existente entre las señales analógicas originales. Estas señales de pulsos, tanto las provenientes de la sección izquierda, como las provenientes de la sección derecha, se correlacionan y se promedian por sección, mediante la integración de una corriente de referencia en un condensador. El voltaje del mismo, resulta proporcional a la duración y cantidad de pulsos que llegan. Para la implementación reportada se eligió que cuando el canal derecho adelante al izquierdo el aumento de potencial sobre el condensador sea positivo. Para el caso contrario se conecta una corriente de referencia en el sentido opuesto, haciendo que disminuya la tensión sobre el condensador. Una vez que se ha

contado una cierta cantidad de pulsos, ya sean provenientes de una u otra línea, se procede a leer el valor de la tensión y restablecer el valor inicial sobre el condensador.

Para la obtención de los pulsos se utiliza un banco de 32 filtros de segundo orden escalados exponencialmente entre 60Hz y 300Hz. Cada sección del filtro está implementada mediante tres amplificadores de transconductancia y dos condensadores. Mediante la variación de la corriente de polarización de los amplificadores se obtiene la modificación de la frecuencia del filtro.

Los resultados experimentales de este esquema implementado en tecnología CMOS de  $0.5 \mu m$  indican un consumo de  $370 \mu A$  a 5V, aproximadamente 2mW, de los cuales  $400 \mu W$  corresponden a los filtros tipo cóclea. Las mediciones reportadas por los autores muestran una desviación estándar que varía entre 2 y 10 grados, en todo el rango de medición.

#### Algoritmo de gradiente espacial (SGA)

Otro enfoque en la localización de fuentes sonoras es el algoritmo del gradiente espacial [19]. Este algoritmo hace otra interpretación de las señales que llegan a los micrófonos, considerando que se está haciendo un muestreo espacial de la onda acústica del sonido. Esta interpretación busca obtener una estimación de la dirección de arribo del sonido en tres dimensiones; en particular, busca una representación por un ángulo de elevación y un ángulo horizontal.

La localización se realiza calculando el gradiente de la onda, para lo cual se necesita la información de amplitud de los cuatro micrófonos al mismo tiempo (ver Fig 1.1). En la resolución del problema se utilizan las derivadas de las señales y las diferencias entre ellas a través de un algoritmo LMS que realiza una regresión lineal.

En la arquitectura del CI se presentan tres bloques fundamentales: etapa de amplificación y diferenciación, etapa de supresión de modo común y estimación de los ángulos. Se realiza un procesamiento analógico para la obtención de las diferencias y derivadas. Para el cálculo de los gradientes se utilizan capacitores conmutados con doble muestreo, obteniéndose con esto un rechazo mayor para el "feedtrough" del reloj y la fuente de alimentación. Además, se utilizan amplificadores implementados con inversores "cascode" para una alta ganancia y un área reducida.

Con esta arquitectura se implementó un CI en tecnología CMOS 0,5µm que presenta una resolución de 2µs para una frecuencia de muestreo de 2KHz; todo esto con una disipación de potencia de 32µW. Las mediciones reportadas por los autores muestran una desviación estándar que varía entre 1 y 4 grados, en todo el rango de medición.

#### Realizaciones en silicio

En el trabajo [7] se presenta una comparación de estos métodos en un marco común, utilizando el mismo conjunto de señales experimentales. La comparación fue hecha a través de simulaciones sobre datos experimentales relevados con la misma interfase analógica. Los resultados numéricos presentados permiten hacer una comparación cuantitativa entre los algoritmos. En la Tabla 1.1 se muestran los valores de desviación estándar reportados para cada algoritmo. Además, se presenta una cota mínima de error (Cramer-Rao) sobre la estimación del retardo y el ángulo de arribo. Dicha cota, calculada en base al espectro de las señales y la ventana temporal de datos, tiene un valor de 0,33º para las condiciones y señales del experimento.

Tabla 1.1: Precisión de los algoritmos (desvío estándar).

| Rar  | igo  | CA    | CCD   | SA    | SG    |

|------|------|-------|-------|-------|-------|

| 0°-1 | 180° | 1,18° | 1,18° | 1,47° | 0,87° |

| 0°-1 | 10°  | 0,85° | 0,85° | 1,05° | 0,25° |

Se desprende de la Tabla 1.1 que no existe diferencia apreciable en la precisión del algoritmo de la derivada de la correlación y el algoritmo de la correlación. También se puede notar la diferencia entre los algoritmos de correlación y el de gradiente espacial, siendo este último el que presenta mejor precisión.

Las características principales de las implementaciones en silicio de los algoritmos presentadas en [11], [17] y [19] se resumen en la Tabla 1.2.

Tabla 1.2: Comparación entre implementaciones de los algoritmos.

| CI                         | Potencia (µW) | Tecnología (µm) | Área       | Precisión |

|----------------------------|---------------|-----------------|------------|-----------|

| Derivada de la correlación | 600           | 0,35            | 2 x 2,4 mm | 5µs       |

| Neuromórfico               | 1850          | 0,5             | 5 x 5 mm   | 2μs       |

| Gradiente espacial         | 32            | 0,5             | 3 x 3 mm   | 2µs       |

La realización basada en el método de gradiente espacial es la que muestra el menor consumo, sin embargo es necesario tener en cuenta que por su implementación a capacitores conmutados no escala con la tecnología, y que la necesidad de evaluar derivadas sobre señales analógicas, es un factor que puede introducir errores ante señales ruidosas.

#### Descripción del CI CCD

Como ya se explicó, una de las técnicas para medir el desfasaje entre dos señales consiste en realizar la correlación temporal entre ellas y encontrar el instante donde se produce el valor máximo. Este método requiere un área importante para su realización en un CI. Sin embargo, si se realiza una aproximación de primer orden a la correlación discreta y se busca el cero de su derivada, se obtiene una reducción significativa en la complejidad de la solución. En este caso sólo se requiere de contadores ascedentes/descendentes y una lógica de decodificación. Por otro lado, si sólo se realiza un cambio sobre los contadores cuando se detecta un cambio de los valores de las entradas, se reduce dramáticamente la actividad del circuito (en la misma relación de la frecuencia de reloj a la frecuencia de la señal de entrada, esto es: 400KHz/200Hz=2.000). Esto, a su vez, produce una reducción del consumo de potencia por el mismo factor.

En esta sección se describe un circuito integrado que es una versión modificada del circuito integrado reportado en [11]. Los resultados experimentales del mismo son parte de esta tesis [20], y se reportan en el Cap. 3. El diseño se basa en una estructura que es capaz de funcionar cuando se conectan en cascada varios CI básicos. Esto permite ampliar el rango de medida o la precisión de la misma, según la conexión que se realice entre los CI básicos.

El CI tiene dos señales de entrada; una de ellas, D-Din, es retardada internamente y la otra, D-Nin, no. Ambas entradas ingresan a los bancos de contadores como se indica en la Fig. 1.4.

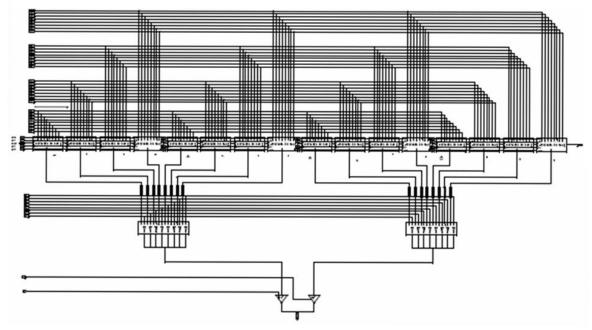

Figura 1.4: Estructura del CI mostrando la cadena de retardos y los contadores ascendentes/descendentes.

Previo a la entrada de cada contador existe un bloque encargado de generar las señales que indican si se debe sumar (UP) ó restar (DN) una cuenta al estado actual del contador k-ésimo. La secuencia generada sigue la siguiente ley:

- a) Sumar uno si D-Nin=1 y D-Din cambia de 1 a 0.

- b) Restar uno si D-Nin=1 y D-Din cambia de 0 a 1.

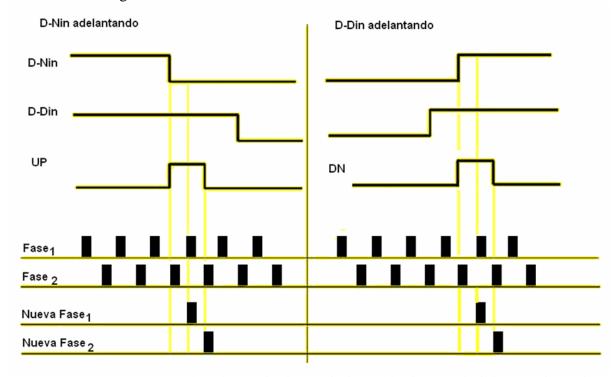

En este mismo bloque se producen dos nuevas señales de reloj (bifásicas), que sólo manifiestan actividad cuando existe un cambio en las entradas. Las diversas señales se muestran en la Fig. 1.5.

Figura 1.5: Diagrama temporal con las señales de entrada, las señales de comando de los contadores y las nuevas señales de reloj.

La estructura principal del chip consiste de 64 contadores ascendentes/descendentes de 10 bits con signo, donde cada uno de ellos es controlado por señales UP y DN que se generan locamente como una operación lógica de las señales a medir que están presentes en cada bloque y el reloj del sistema. Los contadores adyacentes tienen sus correspondientes bits de signo conectados a compuertas XOR que calculan la diferencia entre ellos. La compuerta de que tenga un 0 en su salida indicará que los contadores adyacentes tienen estados con el mismo signo; cuando la salida de una compuerta este en 1 indicará que existe un cambio de signo en los estados y por ende un cruce por cero de la derivada de la función correlación. Recordemos que esto es válido solamente para señales produzcan una función correlación con un único máximo, que es el caso de las que provienen de una fuente sonora predominante.

Si se conoce la ubicación de los contadores entre los que existe la diferencia de signo dentro la cadena de retardos, se puede saber cual es el retardo que hay entre las señales a medir. Para decodificar la ubicación de los contadores se utiliza un decodificador con prioridad de 6 bits. Esto hace que se elija el contador con la posición de menor retardo, en caso de que existan en la cadena de contadores otros cruces por cero. El valor relativo de retardo entre señales es cantidad de retardos que hay hasta el contador seleccionado. Dicho valor multiplicado por el período del reloj de las cadenas retardo da el valor absoluto (en segundos) del retardo entre señales. El valor relativo del retardo se comunica al exterior del CI por medio de buffers tres estados conectados a un bus de datos. Cuando se obtiene un resultado válido se generan dos salidas de habilitación, EO y GS. La señal EI es la habilitación general del CI y debe estar en 0 para que este realice el cálculo; además se utiliza para habilitar al siguiente CI cuando se conectan varios en cascada. En la Tabla 1.3 se presenta una tabla de verdad donde se puede ver el estado de funcionamiento un CI según el valor de estas señales.

Tabla 1.3: Tabla de verdad del funcionamiento de un CI CCD.

| EI | Estado    | GS | ЕО | Bus     |

|----|-----------|----|----|---------|

|    |           |    |    | externo |

| 1  | XXX       | 1  | 1  | Tercer  |

|    |           |    |    | estado  |

| 0  | No        | 1  | 0  | Tercer  |

|    | detección |    |    | estado  |

| 0  | Detección | 0  | 1  | Activo  |

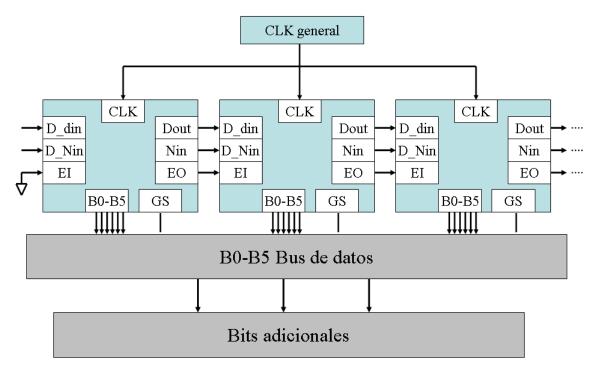

El funcionamiento en cascada de estos circuitos integrados es el siguiente. El par de señales a medir ingresan al primer CI, saliendo la que ingresó por D\_Din retardada por 64 FlipFlops a través de Dout, para ingresar al siguiente CI. La señal sin retardar entra por D-Nin y sale por Nin sin retardo alguno. Cada CI tiene una habilitación general activa por nivel bajo (EI) y una señal de salida disponible (EO) activa por nivel alto. Estas se conectan de un CI a otro, de forma que no se habilite el siguiente CI si el CI anterior obtuvo un resultado válido en su rango de medida. Mediante las diferentes salidas GS es posible identificar cuál de los CI llegó a un resultado, permitiendo así el cálculo del retardo total.

En la Fig. 1.6 se muestra el conexionado en cascada para varios CI, detallando las señales involucradas.

Figura 1.6: Conexionado en cascada para varios CI.

#### Resumen y Comentarios

Las implementaciones digitales tienen la ventaja que con el avance de la integración (CMOS estándar) se puede exportar el diseño a una nueva tecnología de menor consumo sin tener que realizar cambios sustanciales, solamente una comprobación de reglas de tecnología y funcionalidad. Esto permite que una vez desarrollado y comprobado un algoritmo, este puede ser utilizado como un bloque constructivo de sistemas más complejos (sistema en Chip).

De todos modos, toda implementación de un algoritmo para la medición de retardo deberá contar con una etapa de adecuación de señal que respete las restricciones de precisión y ancho de banda que imponga la aplicación particular. El escalado o cambio de tecnología en esta etapa no garantiza una disminución directa del consumo, ya que al tratarse de un diseño analógico existe un compromiso entre ganancia, área y potencia que depende de las especificaciones a cumplir.

El enfoque adoptado en esta tesis se concentra en el diseño de un algoritmo digital más eficiente (respecto a consumo de potencia) que los algoritmos ya presentados en la literatura manteniendo o mejorando la precisión de la estimación.

### Capítulo 2

# Estimador de Tiempo Basado en Correlación

#### Introducción

En el capítulo anterior se describió un algoritmo reportado en [7] para la medición del tiempo de retraso relativo entre dos señales utilizando un método de correlación. En [10] se informaron además mediciones experimentales que confirman la precisión y el bajo consumo del circuito integrado asociado. En el presente capítulo, que constituye la principal contribución de esta tesis, se presenta un algoritmo que permite mejorar las prestaciones de consumo y que resulta equivalente en condiciones de estado estacionario al esquema anterior. El algoritmo se basa en un esquema adaptivo, que propone una señal de error basada en el signo de la diferencia de los desfasajes de las señales de entrada. Se propone un algoritmo de adaptación que garantiza convergencia, y produce una implementación de mínima complejidad en términos de área de silicio. El circuito resultante se fabricó en dos tecnologías diferentes, ambas CMOS estándar, una de 0,5 µm y otra de 0,35 µm ([22],[23],[27]).

Este capítulo se organiza de la siguiente manera. En primer lugar se describe el algoritmo haciendo énfasis en el procesamiento digital de las señales. A continuación se describe la arquitectura empleada para el diseño del circuito integrado. En las dos últimas secciones se desarrollan en detalle los dos circuitos integrados realizados. Se concluye realizando una comparación con otros medidores basados en correlación.

#### Descripción del Algoritmo

El algoritmo procesa información digital proveniente de una etapa de adecuación y conversión de señales analógicas; por lo tanto, de aquí en adelante cuando se hable de señales se estará haciendo referencia a señales de tipo digital.

El primer objetivo en el diseño del nuevo algoritmo es obtener la misma precisión que las implementaciones previas del CCD, con una implementación de menor carga computacional. El algoritmo trabaja con una representación de un bit para las dos señales a procesar, de igual

manera que el CCD, en el cual el retardo entre las señales se obtiene a través de la posición del cambio de signo de mayor prioridad en las salidas de los bancos de contadores. La estrategia que se propone para el nuevo algoritmo es utilizar solamente un contador dentro de un lazo de realimentación, provisto de lógica de control. La presencia de un lazo de control hace que la cuenta del contador converja al valor de retardo existente entre las señales. La reducción del consumo de potencia es consecuencia de la disminución de la cantidad de lógica y de la utilización eficiente de la información presente en las señales de entrada. El algoritmo tiene dos bloques principales donde se realiza el procesamiento: un bloque está encargado de adquirir y retener parte de las señales que ingresan al sistema y el otro bloque está encargado de calcular el retardo. En la Fig. 2.1 se puede ver la conexión entre estos bloques y las señales que los relacionan.

Figura 2.1: Conexión lógica entre bloques del algoritmo.

El retardo que procesa el sistema es el existente entre las señales X1 y X2; provenientes de los micrófonos M1 y M3 que están captando la onda acústica generada por la fuente sonora, como se explicó en el Capitulo 1,. Estas entradas son muestreadas cada Ts segundos, obteniendo así una versión discretizada con una resolución temporal fija. Por esta razón la medición de tiempos no puede ser menor a Ts segundos y el sistema trabaja solamente con tiempos discretos cuyos valores son enteros.

El algoritmo está continuamente monitoreando la actividad de las señales X1 y X2. Cuando se detecta un cambio de estado en ellas, se evalúa si dicho cambio corresponde a una transición válida a ser computada. De ser así, se realiza una acción de cambio de estado de un contador. Dependiendo del estado actual del contador y del tipo de transición de la entrada, corresponderá una u otra acción sobre el contador. El estado del contador indica cual es el retardo que existe entre las señales. El hecho de analizar primero la validez de la transición en las entradas y luego realizar una acción hace que sólo una parte del sistema tenga que estar activa, llevando a una disminución de la actividad total y por consiguiente a una disminución del consumo. La necesidad de muestrear y adquirir parte de las señales para que puedan ser

procesadas por el algoritmo determina que exista un consumo basal. La reducción de dicho consumo basal es tenida en cuenta en la arquitectura e implementación del algoritmo.

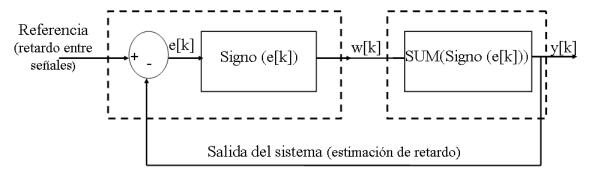

Para el caso de señales de audio, el muestreo se hace a una velocidad mucho mayor que la de las señales, igual al mínimo retardo que se pretende medir. Por ello, se puede considerar que el retardo que existe entre ambas señales se mantiene constante durante el tiempo de cálculo. Siendo esto así, se puede considerar que el sistema está formado por dos bloques en cascada con una realimentación entrada-salida (ver Fig. 2.2). El primer bloque tiene como entradas una estimación de retardo y el retardo actualmente existente entre X1 y X2. Internamente se calcula la diferencia entre las entradas, siendo la salida de este bloque el signo de la diferencia que existe entre estas magnitudes. De la comparación se puede obtener un valor negativo, positivo o nulo. El segundo bloque es un acumulador que suma el signo del error, haciendo que su estado aumente si las contribuciones son positivas, mantenga el valor actual si son nulas o disminuya su estado para valores negativos.

Figura 2.2: Sistema de lazo cerrado para estimación de de retardo.

El sistema se puede ver, Fig. 2.2, como un sistema de control donde el retardo entre las señales, que actúa como señal de referencia del algoritmo de control es la entrada, y el estado estimado del retardo es la salida. El bloque de control actúa para llevar la salida al valor de la entrada. Se puede ver inmediatamente después del detector del error un bloque que implementa la función signo del error. Esta es la función que se implementa en el sistema mediante un bloque digital que al detectar un flanco en una de las entradas, verifica si la otra entrada es positiva o negativa. Esto produce un índice de adelanto o atraso de una entrada respecto a la otra, es decir, que produce el signo del retardo. La señal de error e[k] proviene de la diferencia entre la entrada y la salida del estimador. Un bloque aplica la función signo sobre el error dando como salida el signo del error, w[k]. A continuación se realiza la acumulación o suma de signo del error; esta operación genera la estimación del retardo y la salida del sistema y[k].

Suponiendo que la dinámica del sistema de lazo cerrado es mucho más rápida que la dinámica de la señal de entrada, el sistema puede considerarse con entrada constante. Esto es,  $\tau[k] \in \mathbf{Z}, \ \tau[k] \cong cte$ , a partir de lo cual se pueden escribir las siguientes ecuaciones que rigen el sistema:

$$e[k] = \tau[k] - y[k]$$

$$w[k] = sign(e[k])$$

$$y[k] = sum(w[k]) = y[k-1] + w[k]$$

$$y[k] = y[k-1] + sign(\tau[k] - y[k])$$

(2.1)

Reemplazado la función signo definida como:

$$sign[k] = \begin{cases} +1 & \text{para } k \ge 1\\ 0 & \text{para } k = 0\\ -1 & \text{para } k \ge 1 \end{cases}$$

(2.2)

se llega a que la salida del sistema puede ser descripta por la siguiente ecuación no lineal a diferencias:

$$y[k] = \begin{cases} y[k-1]+1 & \text{para } \tau[k] > y[k] \\ y[k-1] & \text{para } \tau[k] = y[k] \\ y[k-1]-1 & \text{para } \tau[k] < y[k] \end{cases}$$

(2.3)

Un simple análisis de estabilidad de variable discreta muestra que el sistema es estable, y converge al menos en e[k0] muestras, donde e[k0] es la diferencia entre el estado inicial y el retardo de referencia ( $e[k0] = \tau[k0] - y[k0]$ ).

Dado un retardo  $\tau[k]$  entre las señales y con el sistema acumulador partiendo del reposo (valor inicial igual a cero), el error entre la referencia y el valor del acumulador es igual a  $\tau[k]$  y el signo del error positivo. En este caso, como se ve de (2.3), el valor del acumulador aumenta en una cuenta. Esta evaluación y acción se produce hasta que el valor del acumulador iguala al valor de la referencia. En caso que el error resulte negativo se produce una disminución en el valor del acumulador hasta llegar a la igualdad. Para los casos en que la referencia no es un número entero, el sistema queda oscilando en torno al valor de la misma. En la Fig. 2.3 se puede ver un ejemplo de esta convergencia.

En el caso de un retardo negativo, el sistema reacciona de manera similar, sólo que en este caso disminuye el valor del acumulador hasta alcanzar el valor de referencia negativo.

Para poder obtener una cota mínima del tiempo de convergencia, se debe recordar que el algoritmo sólo computa cuando existe actividad en sus entradas (X1, X2), es decir que parte del procesamiento depende de la frecuencia de la señal de entrada. Otra parte del procesamiento depende de la frecuencia de muestreo. Si se considera que por cada período de las entradas se pueden realizar dos cómputos del algoritmo (cuando ocurren los flancos ascendente y descendente), cuando el retardo proviene de señales periódicas sin ruido se puede obtener una expresión sencilla para el tiempo de convergencia. Este tiempo depende del retardo entre señales, el periodo de las mismas y el tiempo de muestreo del sistema, tal como se expresa en (2.4).

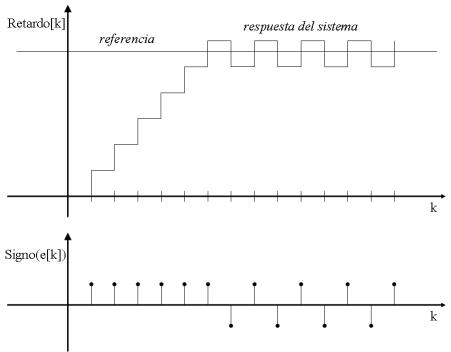

Figura 2.3: Ejemplo de convergencia del sistema.

$$T_{convergencia} = \frac{1}{2} * \frac{T_{se\bar{n}al}}{T_s} * \left| Retardo_{actual} - Retardo_{nuevo} \right|$$

(2.4)

Para obtener una expresión de la velocidad de seguimiento del sistema se puede suponer, sin perder generalidad, que el sistema parte del reposo con condiciones iniciales iguales a cero, esto es:

$$y[k] = 0 \qquad \forall k \le 0. \tag{2.5}$$

Si se supone un retardo variable descripto por una variación lineal

$$Retardo_{\text{variable}} = \tau_0 + ak \tag{2.6}$$

donde  $\tau_0 > 0$  y a > 0, entonces, el sistema tendrá un error positivo por lo que de acuerdo con (2.3) su salida será:

$$y[k] = y[k-1]+1$$

para  $\tau[k] > y[k]$  (2.7)

La ecuación (2.7) puede simplificarse ya que en este caso el sistema se está comportando como un acumulador:

$$y[k] = k \qquad para \ k > 0. \tag{2.8}$$

Despejando el tiempo para el cual el sistema alcanza al retardo referencia, se obtiene:

$$y[k] = Retardo_{\text{var}iable}$$

$$k = \tau_0 + ak$$

$$k = \frac{\tau_0}{(1-a)}$$

(2.9)

Como k debe ser positivo y  $\tau_0$  está definido positivo, el denominador deberá ser positivo.

$$\begin{array}{c}

1 - a > 0 \\

\hline

1 > a

\end{array}

\tag{2.10}$$

De (2.10) se puede concluir que la variación del retardo deberá ser menor que la unidad, para que el algoritmo lo pueda seguir. Relacionando esto con el tiempo de muestreo, el retardo que existe entre las dos señales no podrá cambiar en más de un periodo de muestreo por transición de las señales. Más adelante veremos que el algoritmo sólo computa cuando hay una transición válida en las señales a medir. En la Fig 2.4 se ilustra el seguimiento del algoritmo.

Figura 2.4: Ejemplo de seguimiento de retardos variables.

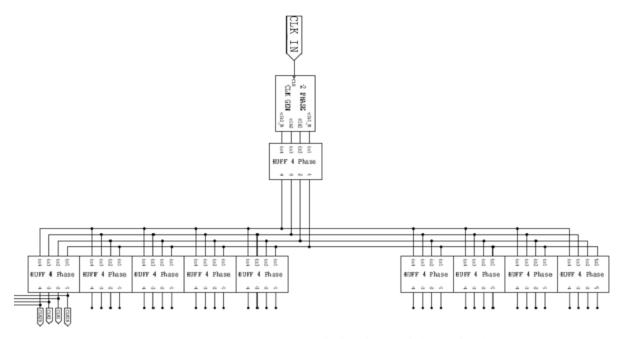

#### Arquitectura del Sistema

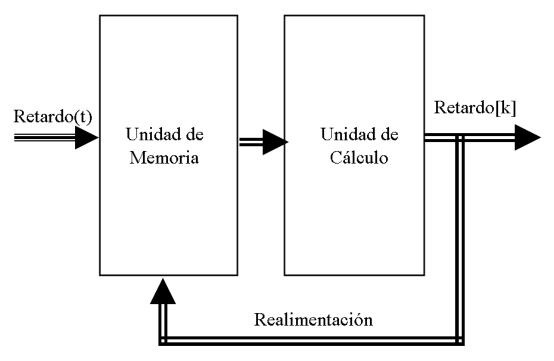

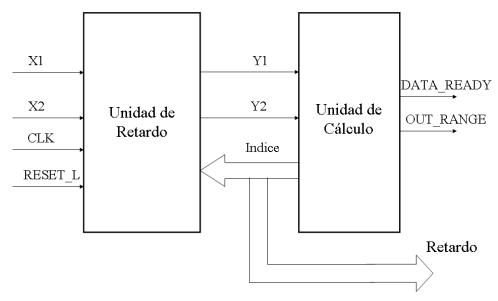

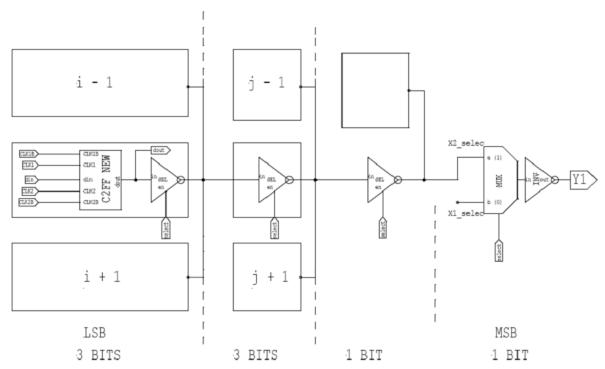

La arquitectura está compuesta por dos bloques principales. Uno de ellos, es la Unidad de Retardo que adquiere las señales de los dos canales y las va almacenando en una serie de registros de paso, para su posterior direccionamiento por la unidad de cálculo. El otro bloque, llamado Unidad de Cálculo, posee un contador y lógica de decisión para producir una estimación del retardo entre las señales a partir de las señales medidas y el valor anterior de la estimación del retardo.

Un diagrama en bloques se muestra en la Fig. 2.5.

Figura 2.5: Diagrama en bloque del sistema.

A continuación se describen ambos bloques en detalle.

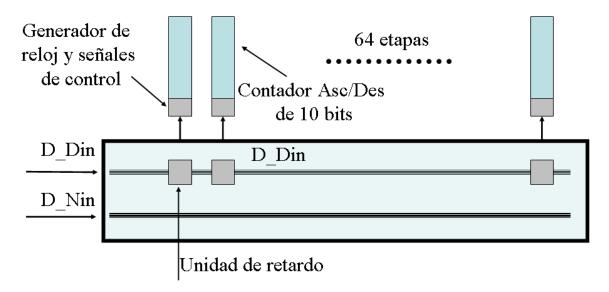

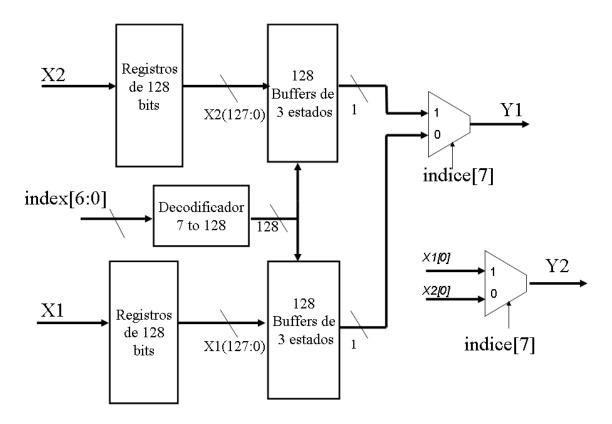

#### Unidad de retardo

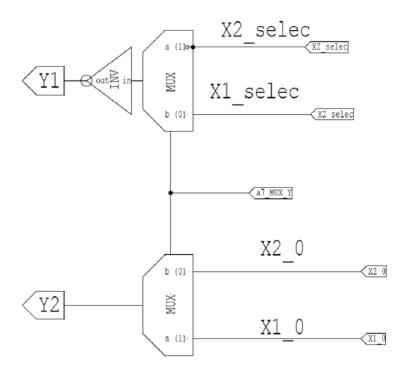

En la unidad de retardo ingresan las señales a medir, el reloj del sistema y las señales de control. Sus salidas son versiones retardadas de las señales de entrada, por lo cual se debe proveer al sistema de memoria. La velocidad a la que se puede grabar y leer esta memoria es un ciclo de reloj. El sistema almacena 128 muestras de cada una de las señales, muestreadas a 1/Ts Hz, donde Ts es la resolución temporal de la medición del retardo. La señal que se toma como referencia es almacenada, y por lo tanto retrasada, en una unidad de memoria con entrada serie y salida paralelo. La información dentro de esta memoria puede ser accedida a través de una palabra de 8 bits. Esto indica que se tiene una memoria de 256 bits. La unidad está compuesta por dos cadenas de 128 registros que tienen sus salidas conectadas a una compuerta inversora con salida tres estados, lo que permite realizar una selección del dato a través de una sencilla decodificación de posición que indica cual es el registro seleccionado. Esta cadena de registros forma un registro de desplazamiento que evoluciona a la velocidad de reloj del sistema. La Fig. 2.6 muestra un esquema de la unidad de memoria.

Para contar con una versión actual de la señal, dos multiplexores permiten la selección entre los datos que salen de la memoria y los datos que ingresan a ella. Es decir, se pueden procesar los datos que están pasando por una cadena de desplazamiento y los datos que están ingresando a la otra cadena. La salida Y1 corresponde a los datos de la memoria y la salida Y2 a las entradas. Invirtiendo la selección de los multiplexores se cambia la señal de referencia, permitiendo que se midan retardos negativos. Esto se puede ver en la Fig. 2.6, donde se aprecian dos multiplexores que están controlados por la señal Indice[7]. Mientras esta señal tome un valor lógico igual a uno la versión retardada de X2 se conecta a la salida Y1 y la versión actual de X1[0] se conecta a la salida Y2.

Figura 2.6: Esquema de la unidad de memoria.

El resto de la palabra de dirección (Indice[6:0]) se conecta a un decodificador de 7 líneas a 128 líneas, cuyas salidas se conectan a los buffers con salida tres estados que permiten hacer la selección de datos. Cada uno de estos buffers se conecta a uno de los registros de la memoria. La dirección está representada en complemento a dos con motivo de facilitar los cálculos que realiza el algoritmo. Internamente hay un conversor de complemento a dos a binario seguido de un decodificador que toma el valor de la dirección y lo transforma en una ubicación en la memoria física.

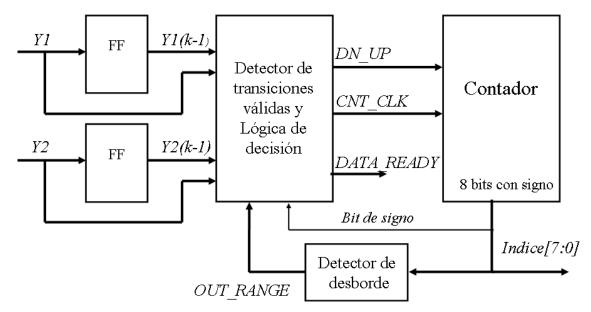

#### Unidad de cálculo

Las salidas de los multiplexores (Y1 y Y2) provenientes de la unidad de memoria se conectan a la unidad de cálculo a través de un "pipeline". El sistema implementa ecuaciones lógicas que evalúan la concordancia de los flancos de la señal retrasada y la señal directa para calcular la función error, a partir de la cual se generan nuevas señales de reloj y control que se alimentan al contador del sistema. Se utiliza un contador de ocho bits en complemento a dos. El esquema de la unidad de cálculo se presenta en la Fig.2.7, donde se pueden ver las señales más importantes.

Figura 2.7: Esquema de la unidad de cálculo.

Las señales provenientes de las cadenas de retardo (Y1 y Y2) son registradas para obtener una versión de las mismas retardadas un sólo ciclo de reloj (Y1(k-1) y Y2(k-1)). Con estas cuatro señales se puede determinar el cambio de flanco que indica que las señales están variando, dando así origen a una sincronización con la actividad de las entradas.

Las ecuaciones Booleanas para el control del contador se obtuvieron mediante la utilización de una herramienta de minimización y síntesis aplicada sobre la tabla de verdad que se muestra en la Tabla 2.1. Las señales de control son el sentido de la cuenta y el reloj para el acumulador. El hecho de usar una nueva señal de reloj para el contador hace que éste sólo trabaje cuando hay un flanco válido en las señales de entrada, produciéndose así una disminución de la actividad del algoritmo.

Tabla 2.1: Tabla de verdad del algoritmo.

| Y1 Y2 estado                        | Signo Acumulador | Acción          |

|-------------------------------------|------------------|-----------------|

| Y1↓                                 | +                | Decremen. Acum. |

| Y                                   | -                | Incremen. Acum. |

| Y2=0                                |                  |                 |

| Y1↓                                 | +                | Incremen. Acum. |

| Y                                   | -                | Decremen. Acum. |

| Y2=1                                |                  |                 |

| Y1↑                                 | +                | Incremen. Acum. |

| Y                                   | -                | Decremen. Acum. |

| Y2=0                                |                  |                 |

|                                     |                  |                 |

| Y1 Y2 estado                        | Signo Acumulador | Acción          |

| Y1↑                                 | +                | Decremen. Acum. |

| Y                                   | -                | Incremen. Acum. |

| Y2=1                                |                  |                 |

| Otras condiciones → Mantener cuenta |                  |                 |

La herramienta de minimización gratuita Expresso, de la universidad de Berkeley produjo el siguiente conjunto de ecuaciones,

$$DN_{UP} = \overline{SGN} * (A+B) + \overline{SGN} * \overline{OVN} * (C+D)$$

$$CLK_{CNT} = \overline{SGN} * \overline{OVP} * (A+B) + SGN * \overline{OVN} * (C+D) + (A+B)$$

(b)

$$A+B = \overline{Y_1} * Y_{1_{-K1}} * \overline{Y_2} * \overline{Y_{2_{-K1}}} + Y_1 * \overline{Y_{1_{-K1}}} * Y_2 * Y_{2_{-K1}}$$

(c)

$$C+D = \overline{Y_1} * Y_{1_{-K1}} * Y_2 * Y_{2_{-K1}} + Y_1 * \overline{Y_{1_{-K1}}} * \overline{Y_2} * \overline{Y_{2_{-K1}}}$$

(d)

donde DN\_UP y CNT\_CLK son las salidas y SGN, OVN, (A+B) y (C+D) son señales internas necesaria para el cálculo. La señal DN\_UP indica al contador que se debe aumentar en uno la cuenta en estado alto ó disminuir la cuenta en estado bajo. Esta señal se puede interpretar como el signo del error, en concordancia con la descripción del algoritmo. La señal CNT\_CLK genera el nuevo reloj para el contador, que si bien sólo está presente cuando hay actividad válida en las entradas, debe estar sincronizado con el resto del sistema. Esta unidad también genera señales auxiliares que indican la validez de los datos presentes en el bus de salida (DATA READY) y si se está en un estado de saturación del contador (OUT RANGE). Cuando la señal está en estado bajo indica que los datos que se tienen en el bus de salida no son válidos, ya que se está produciendo una actualización en el contador. Cuando la señal recupera el valor alto, los datos pueden ser leídos del bus. La señal de OUT\_RANGE se usa internamente para indicar la saturación del contador y establecer una protección que impida el desborde de éste. La unidad de control bloquea la generación de las señales de reloj que van al contador, aunque las señales de DN\_UP se siguen generando. Además, esta señal también puede ser usada externamente para informar a un sistema de jerarquía superior que se debe modificar la velocidad del reloj y realizar una medición con mayor o menor resolución.

Dado que el período del reloj del contador depende de las condiciones de las señales a medir, puede suceder que durante algunos ciclos no existan pulsos de reloj, por lo que se deben emplear registros estáticos para garantizar la perdurabilidad de los estados lógicos. Si se implementan contadores con registros dinámicos se debe garantizar la periodicidad del reloj. El contador utilizado tiene una arquitectura básica de sumador con acarreo de carry y registros estáticos activos por flanco positivo. La actualización del contador se produce en el flanco siguiente al que produjo la condición de cambio, de forma tal que se evitan carreras de datos. El hecho de que su valor solamente cambie en +/- 1 bit garantiza que el sistema no tenga sobrepicos mayores a un (1) bit, lográndose una precisión en el seguimiento de +/- ½ bit. Para una frecuencia de muestreo de 200KHz se obtiene una precisión de +/- 2.5μs.

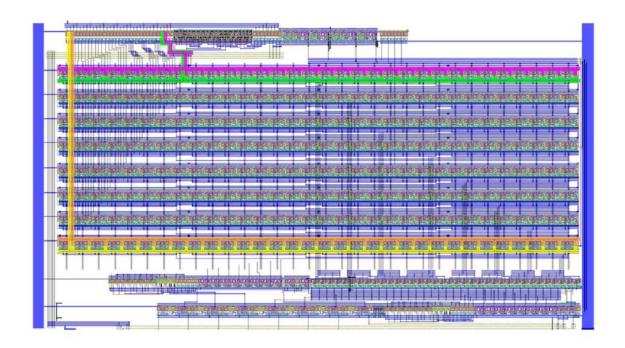

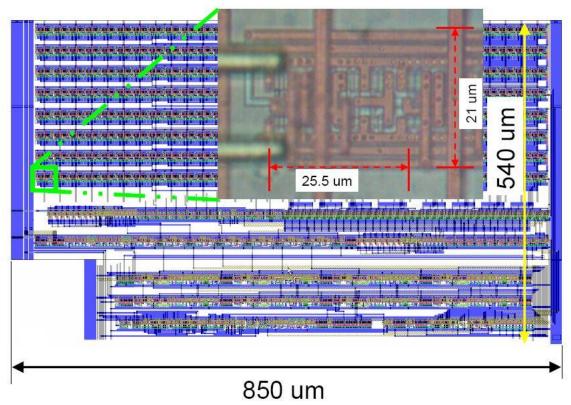

#### Realización del Circuito Integrado

En esta sección se describe la realización de un circuito integrado que implementa el algoritmo descripto. Cabe aclarar que si bien la arquitectura y el diseño se presentan en forma secuencial a lo largo del texto, ambos procesos fueron desarrollados en forma conjunta, dado que toda decisión sobre la arquitectura tiene un impacto directo sobre las prestaciones del circuito integrado. En este sentido, en todo momento se priorizó la reducción del consumo,

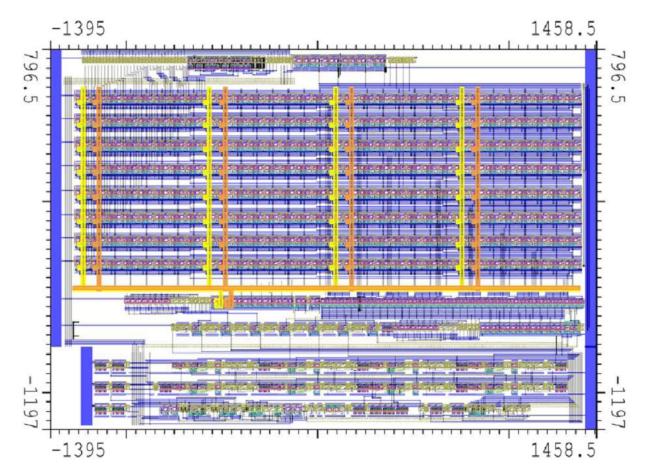

principalmente a través de la reducción de la actividad del circuito. El proceso de diseño se hizo de la siguiente manera. Se comenzó con una descripción lógica del algoritmo en Verilog [21]. A partir de esta descripción se realizó el esquemático del circuito, utilizando el software S-Edit de Tanner®. Sobre la descripción a nivel de transferencia de registros (RTL) se incluyeron modificaciones considerando las restricciones referidas al consumo de potencia. La máscara o "layout" se realizó a partir de este esquemático, por lo cual fue necesario diseñar cada una de las celdas básicas de la librería. Con el layout final, se realizó una extracción del circuito incluyendo capacidades parásitas de los transistores, que luego fue simulada sobre Eldo y Mach-TA Mentor Graphics® para verificar temporizados, estimación de consumo y consistencia de la lógica. El simulador Mach-TA hace una simulación rápida del circuito, utilizando un modelo de llave con resistencia y capacidades para los transistores, y es relevante para detectar problemas de temporizado, carreras e inconsistencia en la lógica. Eldo es un simulador analógico que permite determinar con mayor precisión las respuestas temporales.

El circuito integrado se diseñó originalmente para una tecnología CMOS de 0,5µm y luego surgió la posibilidad de integrar en tecnología CMOS 0,35µm, lo cual originó una segunda versión. Ambas corridas se realizaron utilizando el servicio provisto por MOSIS, a través de sus programas MEP Research. A continuación se describen los puntos esenciales de cada una de las realizaciones.

#### Implementación en Tecnología CMOS de 0,5μm

#### Unidad de memoria

Considerando la velocidad de operación y su tamaño, la unidad de memoria es responsable de la máxima disipación dentro del circuito. Con el objetivo de minimizar este consumo, las cadenas de registros fueron implementadas con registros dinámicos C<sup>2</sup>MOS [24] de ocho transistores. Estos registros maestro-esclavo disparados por flanco no necesitan realimentación, ya que los datos son almacenados en las capacidades de nodo internas, y presentan una baja carga a la línea de reloj (bajo fan-in) además de ocupar un área menor que los clásicos registros maestro-esclavo con realimentación (ver [25], pág. 332).

Figura 2.8: Registro  $C^2MOS$  y compuerta inversora 3 estados.

A la salida de cada uno de estos registros hay un inversor con salida tres estados de tamaño mínimo. El tamaño se elije mínimo para producir un mínimo fan-out en la etapa precedente. En la Fig. 2.8 se puede ver el circuito de uno de estos registros y su compuerta de salida. Este circuito de catorce transistores puede considerarse la unidad de memoria básica.

EL tamaño de los transistores es de W/L=  $3\mu m$  /  $0.6\mu m$  para los PMOS y de W/L=  $1.8\mu m$  /  $0.6\mu m$  para los NMOS. Se destaca que la relación entre el tamaño de los transistores es de 1.66. Esta relación es un compromiso entre la velocidad / margen de ruido de la lógica y el área que ocupa la unidad básica de memoria. Un diseño estándar conduciría a la utilización de una relación de 3 para lograr una igualdad entre capacidades de corriente de los PMOS y los NMOS, y así, un umbral de transición centrado en la tensión de alimentación dividida por dos.

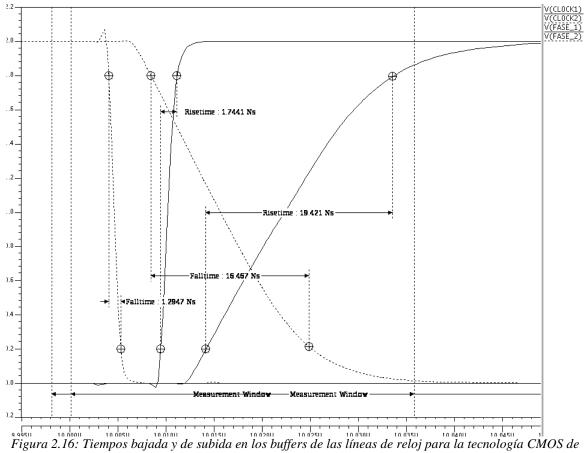

Para determinar los márgenes de ruido de la lógica se procedió a simular la transferencia de una compuerta inversora del tamaño descripto anteriormente. En la Fig. 2.9 se presenta la curva de transferencia para una tensión de alimentación de 3,3V, de donde se observa que el umbral de lógica está en 1,57V.

Calculando la ganancia de la compuerta en torno a ese punto se pueden obtener los márgenes de ruido de la lógica que resultaron ser de 2,35V para el nivel alto y de 1,09V para el nivel bajo.